coshy

Member level 4

Dear All,

I'm trying to make a timing report for all path which is

1. Input to register path

2. Register to register path

3. Register to output path

4. Input to output path

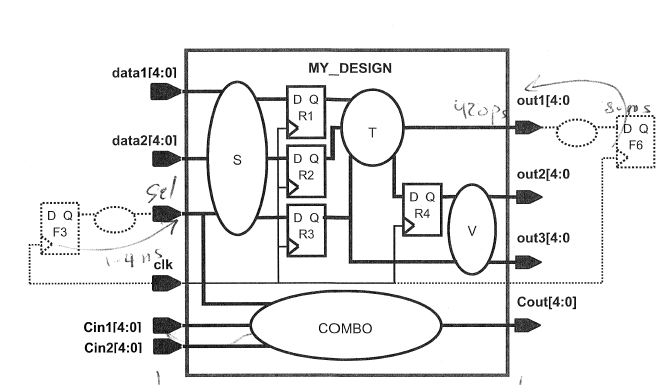

Basically My design is

RTL:

SDC

And I've got the report report_reg2output but it seems something wrong.

Why can't report with any path? Did I something to do wrong?

One thing is for input to output reports.

As you can see the above report, It supposed to report with Cin1[4:0] and Cin2[4:0] to Cout[4:0] path not only sel to Cout[4:0] path. But didn't it.

Would you please help me how to get a path timing Right report ?

I'm trying to make a timing report for all path which is

1. Input to register path

2. Register to register path

3. Register to output path

4. Input to output path

Basically My design is

RTL:

Code:

module MY_DESIGN ( Cin1, Cin2, Cout, data1, data2, sel, clk, out1, out2, out3);

input [4:0] Cin1, Cin2, data1, data2;

input sel, clk;

output [4:0] Cout, out1, out2, out3;

reg [4:0] R1, R2, R3, R4, out1, out2, out3;

wire [4:0] arth_o;

ARITH U1_ARITH ( .a(data1), .b(data2), .sel(sel), .out1(arth_o) );

COMBO U_COMBO ( .Cin1(Cin1), .Cin2(Cin2), .sel(sel), .Cout(Cout) );

always @ (posedge clk)

begin

R1 <= arth_o;

R2 <= data1 & data2;

R3 <= data1 + data2;

R4 <= R2 + R3;

end

always @ (out2, R1, R3, R4)

begin

out1 <= R1 + R3;

out2 <= R3 & R4;

out3 <= out2 - R3;

end

endmoduleSDC

Code:

report_timing -from [all_inputs] -to [all_registers -data_pins] -max_paths 10 > report_input2r.rpt

report_timing -from [all_registers -data_pins] -to [all_registers -data_pins] -max_paths 10 > report_reg2r.rpt

report_timing -from [all_registers -data_pins] -to [all_outputs] -max_paths 10 > report_reg2o.rpt

report_timing -from [all_inputs] -to [all_outputs] -max_paths 10 > report_intput2out.rptAnd I've got the report report_reg2output but it seems something wrong.

Why can't report with any path? Did I something to do wrong?

Code:

****************************************

Report : timing

-path full

-delay max

-max_paths 10

Design : MY_DESIGN

****************************************

Wire Load Model Mode: enclosed

No paths.

1One thing is for input to output reports.

Code:

****************************************

Report : timing

-path full

-delay max

-max_paths 10

Design : MY_DESIGN

****************************************

Wire Load Model Mode: enclosed

Startpoint: sel (input port clocked by clk)

Endpoint: Cout[4] (output port clocked by clk)

Path Group: clk

Path Type: max

Point Incr Path

--------------------------------------------------------------------------

clock clk (rise edge) 0.00 0.00

clock network delay (ideal) 1.00 1.00

data required time 3.75

--------------------------------------------------------------------------

data required time 3.75

data arrival time -1.40

--------------------------------------------------------------------------

slack (MET) 2.35

1As you can see the above report, It supposed to report with Cin1[4:0] and Cin2[4:0] to Cout[4:0] path not only sel to Cout[4:0] path. But didn't it.

Would you please help me how to get a path timing Right report ?