viperpaki007

Full Member level 5

- Joined

- Jul 2, 2008

- Messages

- 274

- Helped

- 11

- Reputation

- 22

- Reaction score

- 8

- Trophy points

- 1,298

- Location

- Finland

- Activity points

- 3,437

Hi,

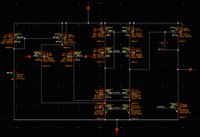

I have made a simple folded cascode structure (Circuit diagram attached). All the transistors are working in saturation. However, i have a small problem. When i put the opamp in unity buffer configuration, the output voltage is at at higher dc-offset. I don't know how to make the dc-offsets and input and output equal. Can anybody help. Simulation results are attached.

I have made a simple folded cascode structure (Circuit diagram attached). All the transistors are working in saturation. However, i have a small problem. When i put the opamp in unity buffer configuration, the output voltage is at at higher dc-offset. I don't know how to make the dc-offsets and input and output equal. Can anybody help. Simulation results are attached.