Young_Electronic_00

Newbie level 5

Hello all,

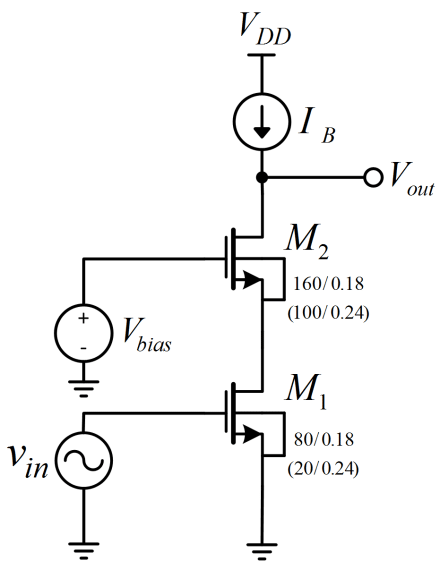

I found some schematic of cascode amplifier:

I'm just wondering why authors used transsistors having different parameters. Such configuration have some advantages in terms of operational banwdwidth or what ?

Best Regads,

Tom

I found some schematic of cascode amplifier:

I'm just wondering why authors used transsistors having different parameters. Such configuration have some advantages in terms of operational banwdwidth or what ?

Best Regads,

Tom