movinghoon96

Junior Member level 1

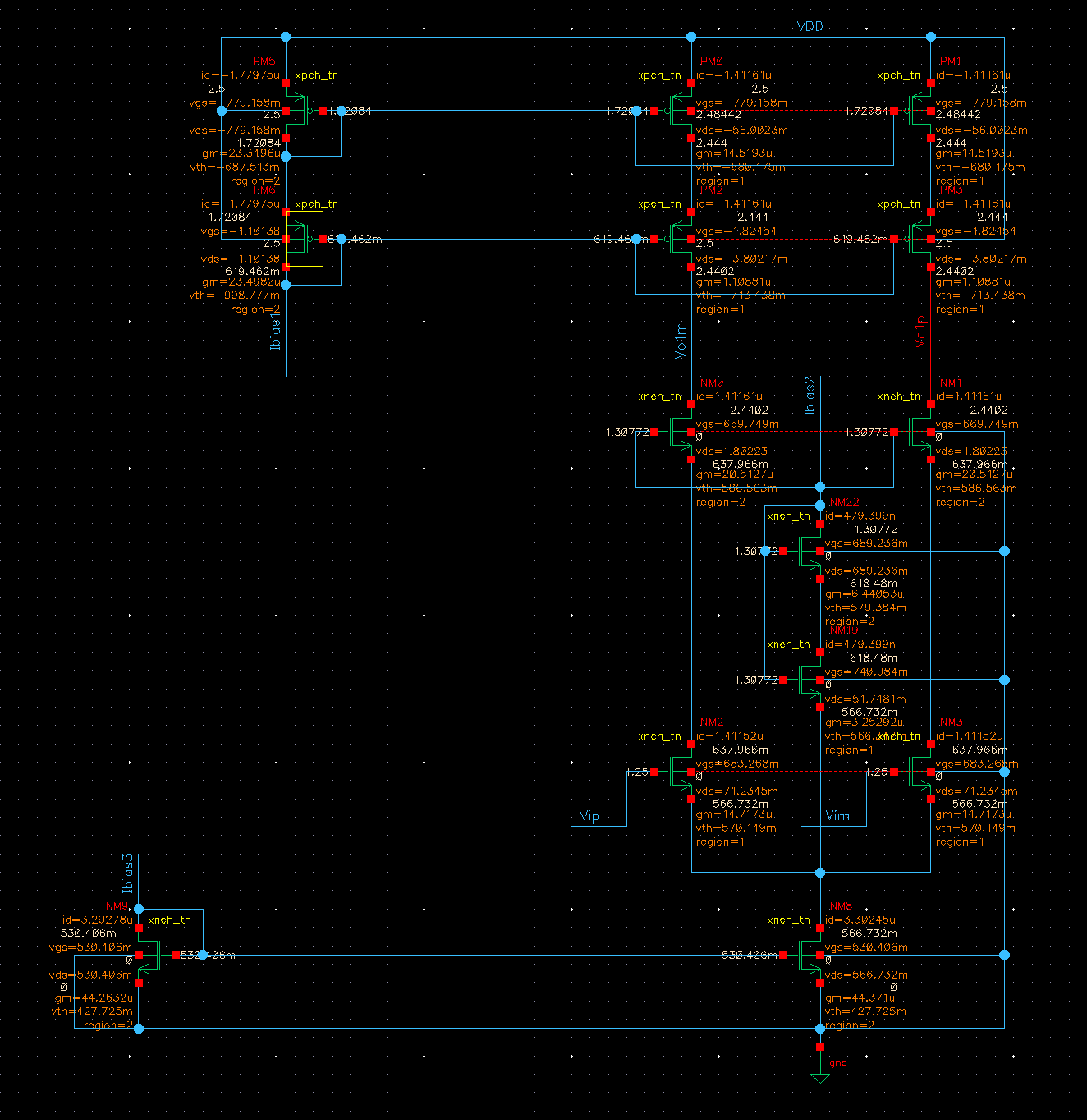

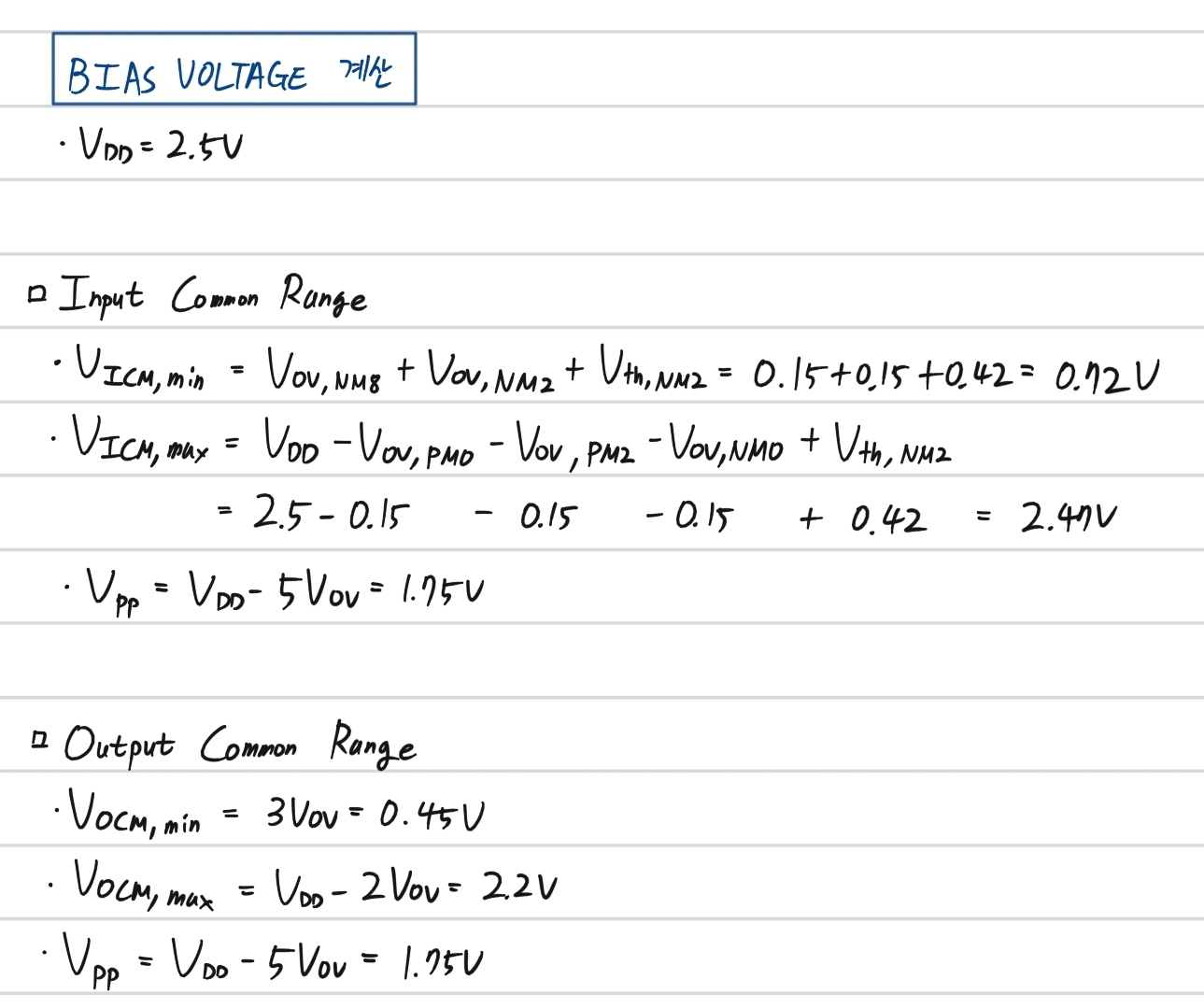

Hello, I'm trying to design Cascode Amplifier. I've spent over 1 week reading textbook to fix this, but couldn't solve it yet. Really need some advice to breakthrough.

MOSFETs are not in Saturation Region, I'd like to know why and how to fix it.

Suggesting Textbook, Article is all OK. Need any clue for it.

[Before Enter]

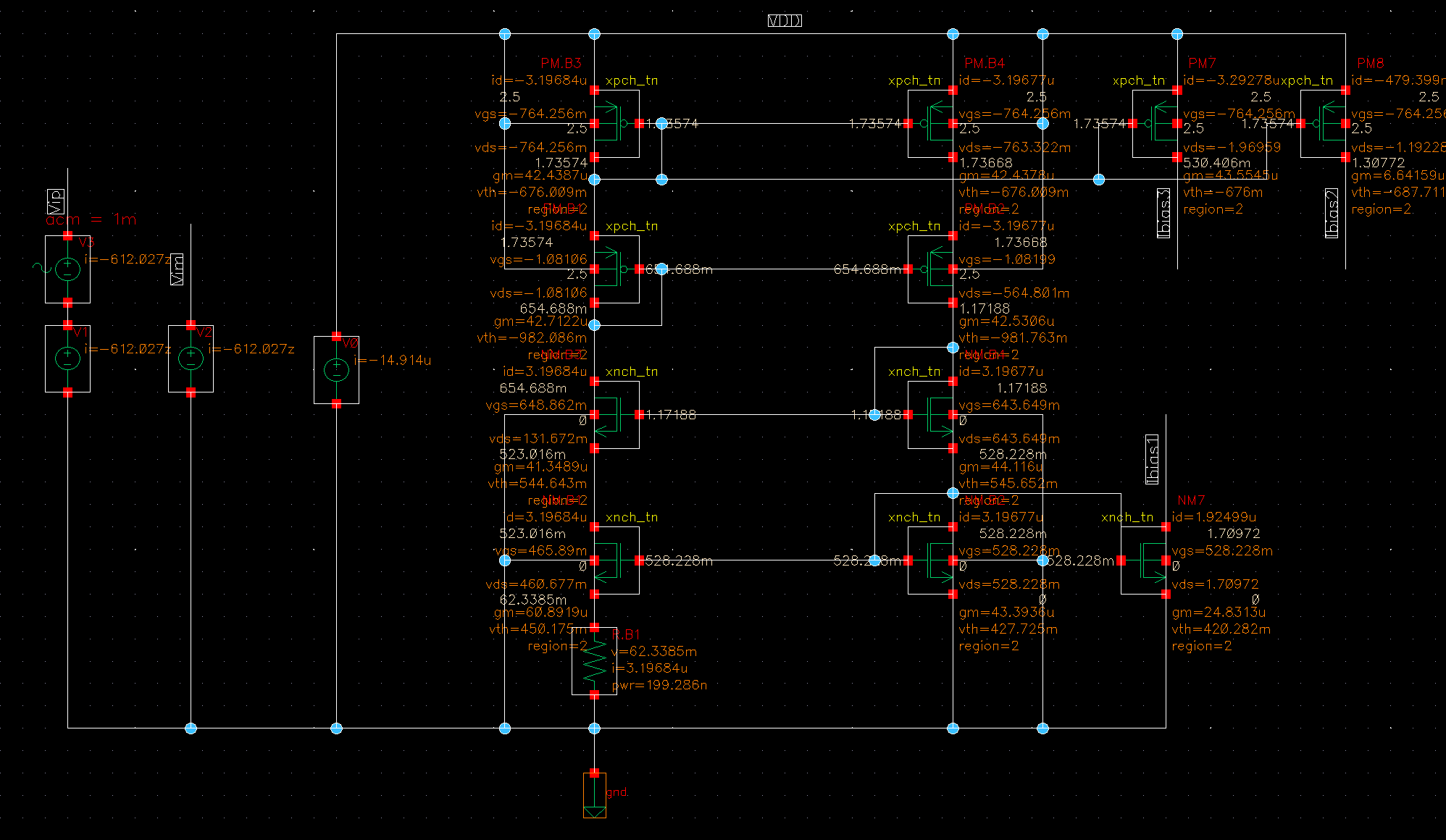

I've already designed simple 2-stage 5OTA - 1 stage : 3uA 2 stage : 100uA

according to slew rate, frequency. it worked fine.

so I choosed 3uA for 1-Stage Cascode Amplifier. and Bias circuit seems working well.

[MOSFET Info]

Process Minimum (W/L) = almost (0.5um/0.5um)

1) NMOS (Vth0 = 0.42)

(W/L) = (2.5um/2um), Id = 1.5uA @ Vgs = 0.52V & Vds = 0.15V

gm = 20uS, ro = 914kohm

2) PMOS (Vth0 = -0.67)

(W/L) = (15um/2um), Id = 1.53uA @ Vgs = -0.77 & Vds = 0.15V

gm = 20uS, ro = 1.6Mohm

① Cascode is not in saturation

I set Input Vi+,Vi- = 1.25V according to hand calculation.

And I got AC Gain = -15dB for 10Hz.

I guess it because my TR is not in saturation.

② Bias Voltage for NM0,1 is not calculated

I found Diode-Connected Device is recommended for level-shifter, requiring current lower than 'real' branches.

But how low? Couldnt find meaningful answer on Sedra&Smith, Razavi's textbook.

MOSFETs are not in Saturation Region, I'd like to know why and how to fix it.

Suggesting Textbook, Article is all OK. Need any clue for it.

[Before Enter]

I've already designed simple 2-stage 5OTA - 1 stage : 3uA 2 stage : 100uA

according to slew rate, frequency. it worked fine.

so I choosed 3uA for 1-Stage Cascode Amplifier. and Bias circuit seems working well.

[MOSFET Info]

Process Minimum (W/L) = almost (0.5um/0.5um)

1) NMOS (Vth0 = 0.42)

(W/L) = (2.5um/2um), Id = 1.5uA @ Vgs = 0.52V & Vds = 0.15V

gm = 20uS, ro = 914kohm

2) PMOS (Vth0 = -0.67)

(W/L) = (15um/2um), Id = 1.53uA @ Vgs = -0.77 & Vds = 0.15V

gm = 20uS, ro = 1.6Mohm

① Cascode is not in saturation

I set Input Vi+,Vi- = 1.25V according to hand calculation.

And I got AC Gain = -15dB for 10Hz.

I guess it because my TR is not in saturation.

② Bias Voltage for NM0,1 is not calculated

I found Diode-Connected Device is recommended for level-shifter, requiring current lower than 'real' branches.

But how low? Couldnt find meaningful answer on Sedra&Smith, Razavi's textbook.