jollorenzo

Newbie

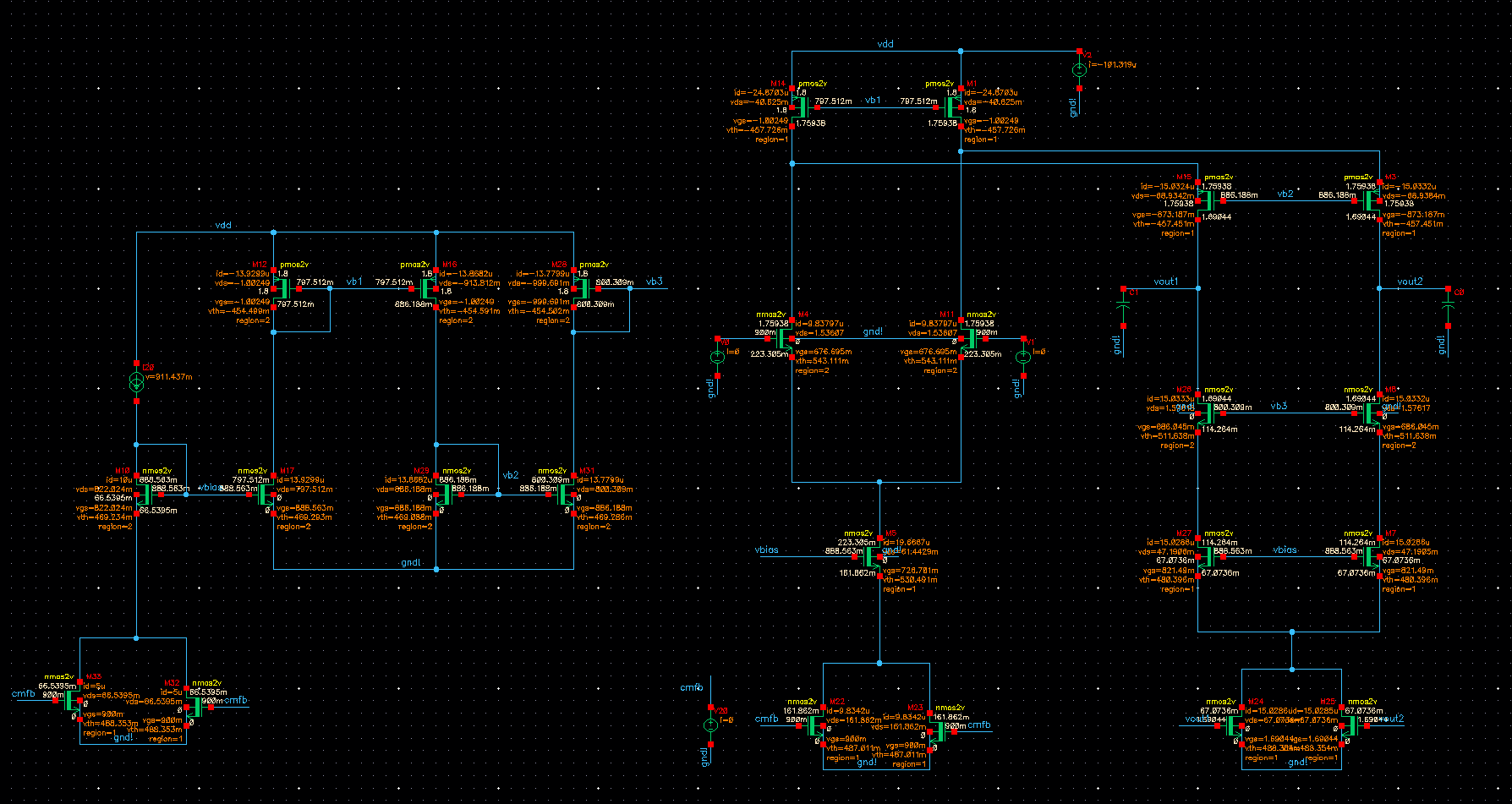

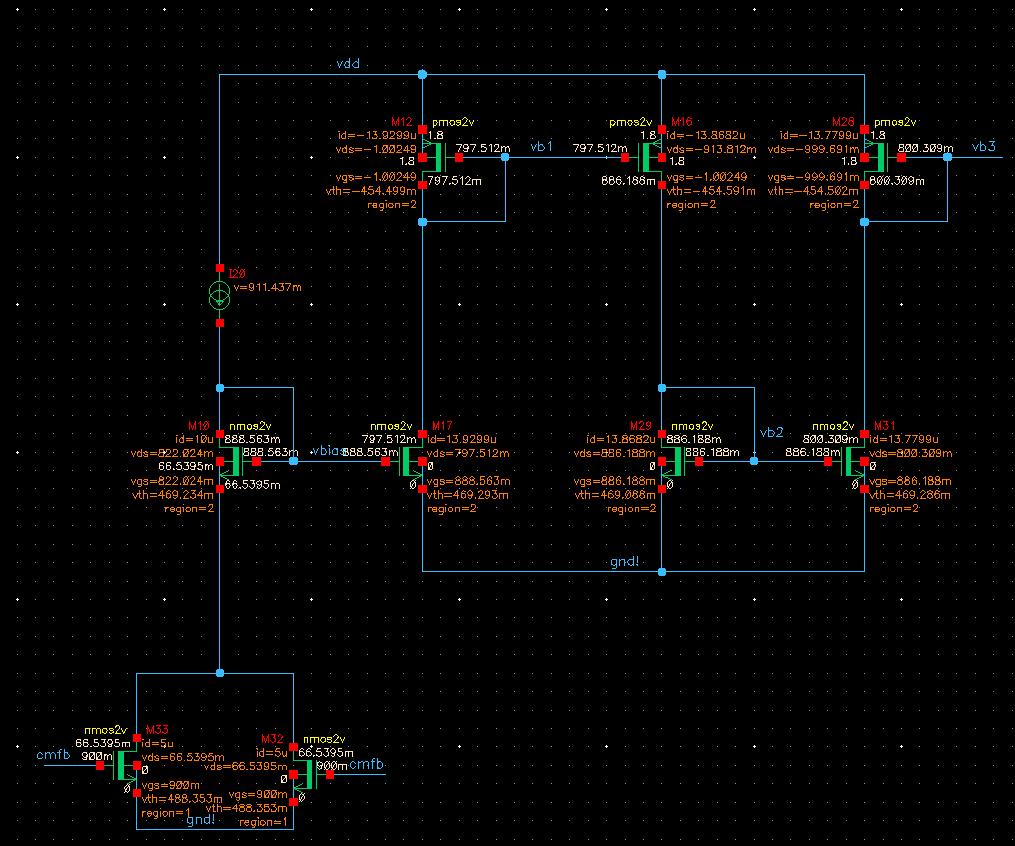

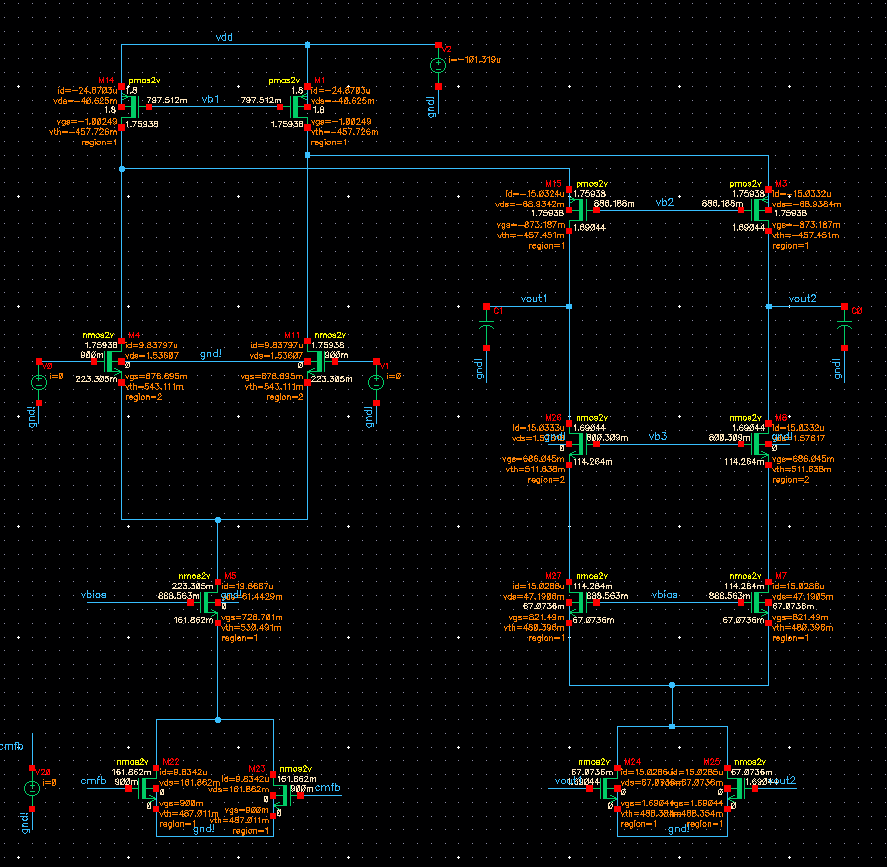

Hi everybody! i have to size all the transistors of a fully diff folded cascode. i have tried for simplicity to use all current mirrors in the biasing circuit 1:1 and to amplify the current only in the folded cascode. I used L = 1u for every transistors, W = 10u for the transistors in the first branch eccept the input ones and W = 5u for the input ones and the ones in the output branch.

logically i supposed that Iout = I1 - Iref/2 where I1 is the current in the two upper transistors in the first branch.

Doing this i will expect an output current equal to the one in the input differential pair but it isnt. i don't know how to size properly the transistors. i also did the math but once in cadence it is all different from the results on paper.

please help me, thank you in advance.

logically i supposed that Iout = I1 - Iref/2 where I1 is the current in the two upper transistors in the first branch.

Doing this i will expect an output current equal to the one in the input differential pair but it isnt. i don't know how to size properly the transistors. i also did the math but once in cadence it is all different from the results on paper.

please help me, thank you in advance.