saqib007

Newbie

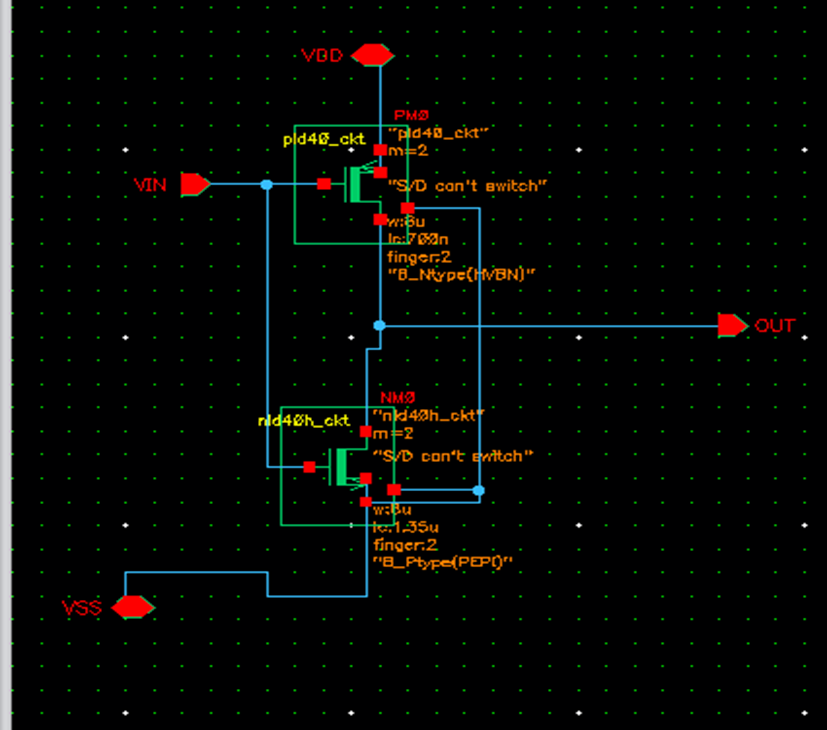

I am facing some issue regarding ERC. i have design a layout of inverter using SMIC 180nmBCD PDK,. i have used high voltage device NLDMOS (nld40h_ckt and pld40h_ckt)

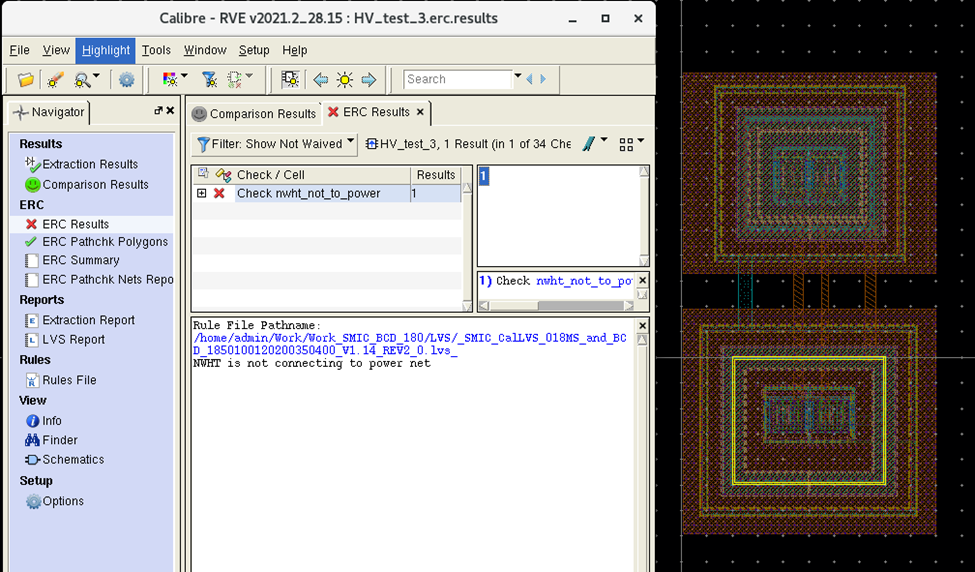

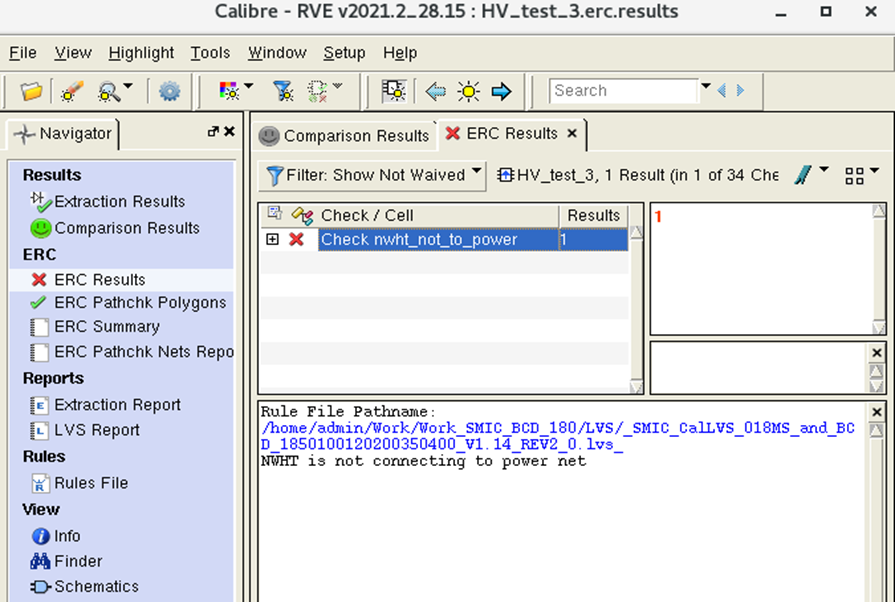

and i got an ERC error mentioned below.

There is NWHT i.e. HVBN layer associated with aforementioned transistor which is basically used for isolation purposes. According to SMIC this layer must be connected to drain of the NLDMOS and when i do so then i face ERC error " NWHT is not connecting to power net" as given in the figure below.

i want the expert's opinion on this matter if whether I can ignore this ERC or there is any solution does exist for it. I expect high voltage layout engineer will present their opinion.

and i got an ERC error mentioned below.

There is NWHT i.e. HVBN layer associated with aforementioned transistor which is basically used for isolation purposes. According to SMIC this layer must be connected to drain of the NLDMOS and when i do so then i face ERC error " NWHT is not connecting to power net" as given in the figure below.

i want the expert's opinion on this matter if whether I can ignore this ERC or there is any solution does exist for it. I expect high voltage layout engineer will present their opinion.