vinayakdabholkar

Advanced Member level 4

Often convergence errors occur when I have 3-terminal devices, and I power them from one supply voltage, yet drive the base/gate from a different voltage. In real life it is not necessarily an error. But the simulator gets confused.

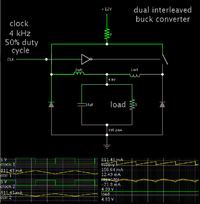

In particular, your buck converter has a 12V supply. The mosfet gates are driven by 20V. There's a chance this causes the error. It would be easier if the simulator would tell us, wouldn't it?

Another possibility: mosfet M2 is N-type. Its gate is referenced to the source terminal. For it to turn on, it needs to see a definite lower volt level at the source terminal. However there are components intervening in the path to ground.

Furthermore when it turns on, it conducts 12V to the node below it, and the node goes to almost 12V. To solve this with real hardware we drive the gate with 20V... But how the simulator interprets it, only the simulator knows.

It may help if you use a P-mos for the high side.

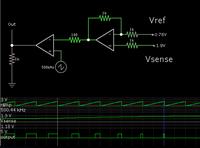

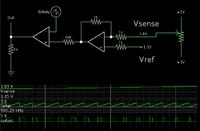

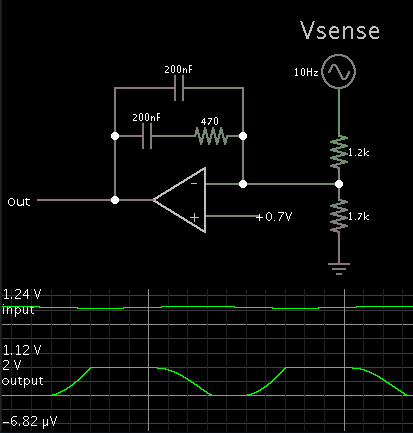

i wanted to know how to connect the output of the comparator lt1016 to M2 whose gate is not referenced to ground but referenced to source, while the output of the comparator is referenced to ground i think. I am attching the schematic again also i have attached the output of the pwm comparator and i think the pwm is not correct i.e when the error is more the pulse width should be more, but here it is less for more error and becomes more for small error.I am not getting where to make the changes for the pwm, tried changing the ramp amplitude,but that may be trial and error.Are there any design equations for this ?