Junus2012

Advanced Member level 5

Dear friends

I an simulating the total settling time of t he operational amplifier. I am connecting it as a buffer and I apply an input pulse. I have no problem to measure the slew rate, but when I tell the calcultaor to calcultae the settling time it take several periods of my signal, why ??

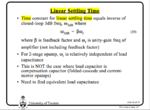

I also would ask you in case if I want to measure the linear settling time under the small signal condition, how much should I apply step voltage so that that the op-amp is not slewing ? also how to measure the propogation time delay ??

thank you in advance

I an simulating the total settling time of t he operational amplifier. I am connecting it as a buffer and I apply an input pulse. I have no problem to measure the slew rate, but when I tell the calcultaor to calcultae the settling time it take several periods of my signal, why ??

I also would ask you in case if I want to measure the linear settling time under the small signal condition, how much should I apply step voltage so that that the op-amp is not slewing ? also how to measure the propogation time delay ??

thank you in advance