tarek1984

Junior Member level 1

Hi

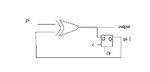

i want to make this

pi = pi ⊕ pi−1

so i tried to use a d-flip flop to store the pi−1 to xor it with the new pi

and i used this verilog code for it

but for some reasons this do not work well

in the beginning i give a clear pulse to the d-ff then i need it give a delayed value of the previous output .

Can any body help me by this verilog code

thanks

i want to make this

pi = pi ⊕ pi−1

so i tried to use a d-flip flop to store the pi−1 to xor it with the new pi

and i used this verilog code for it

module FDC (

D , // Data Input

C , // Clock Input

CLR , // Reset input

Q // Q output

);

//-----------Input Ports---------------

input D, C, CLR ;

//-----------Output Ports---------------

output Q;

//------------Internal Variables--------

reg Q;

//-------------Code Starts Here---------

always @ ( C )

if (~CLR) begin

Q <= 1'b0;

end else begin

Q <= D;

end

endmodule

but for some reasons this do not work well

in the beginning i give a clear pulse to the d-ff then i need it give a delayed value of the previous output .

Can any body help me by this verilog code

thanks

Attachments

Last edited: