EDA_hg81

Advanced Member level 2

Any helps for the following Verilog coding are appreciated.

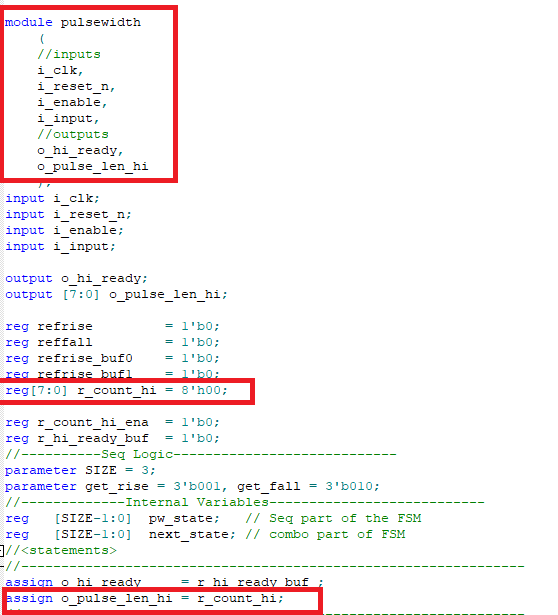

Pulsewidth module is instantiated in top_pll module and the data port will be transferred from pulsewidth module to top_pll module for further processing.

I have defined the data port in pulsewidth module with r_count_hi (define as reg) and r_count_hi is assigned to output port by assign o_pulse_len_hi = r_count_hi;

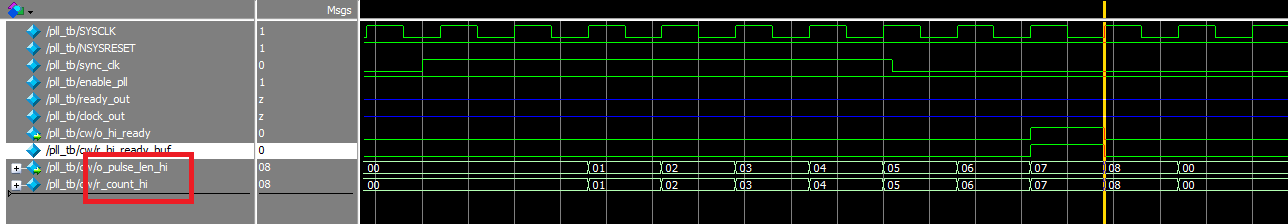

The pulsewidth module can work alone very well as shown in the attached simulation image.

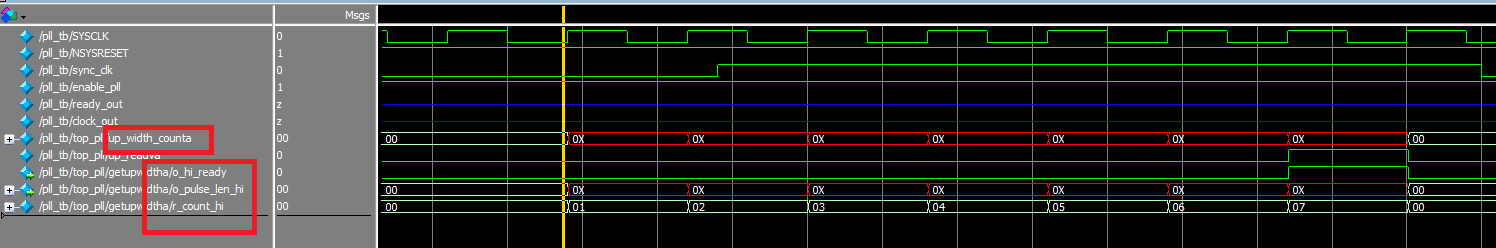

But when combine pulsewidth module with top_pll module, the data port can not be transferred to top_pll module properly as shown in the attached image, I have defined the data input port of top_pll module as wire.

If it is possible, please let me know any problems for above problem.

Many thanks in advance.

I have found the root cause for this problem.

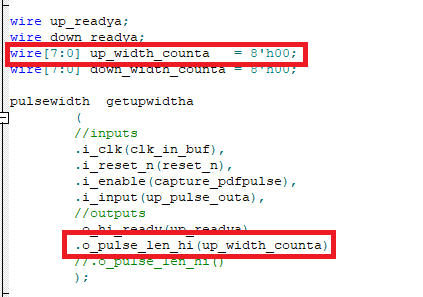

I should not initialized wire[7:0] up_width_counta = 8'b00;

Only need to define as wire[7:0] up_width_counta; will solve the problem.

Pulsewidth module is instantiated in top_pll module and the data port will be transferred from pulsewidth module to top_pll module for further processing.

I have defined the data port in pulsewidth module with r_count_hi (define as reg) and r_count_hi is assigned to output port by assign o_pulse_len_hi = r_count_hi;

The pulsewidth module can work alone very well as shown in the attached simulation image.

But when combine pulsewidth module with top_pll module, the data port can not be transferred to top_pll module properly as shown in the attached image, I have defined the data input port of top_pll module as wire.

If it is possible, please let me know any problems for above problem.

Many thanks in advance.

--- Updated ---

I have found the root cause for this problem.

I should not initialized wire[7:0] up_width_counta = 8'b00;

Only need to define as wire[7:0] up_width_counta; will solve the problem.

Last edited: