sims0702

Newbie level 4

Hey,

I was wondering if I could get some help on the following issue.

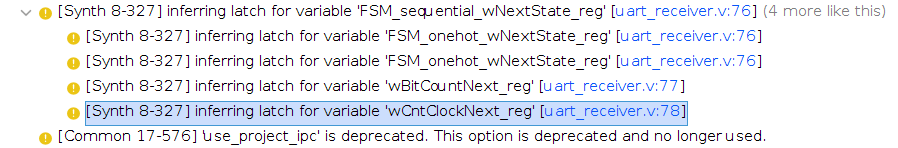

I am getting latches for the registers shown in the picture and I can't figurer out why that is the case. It is a uart_rx module with an FSM. When determining the next state logic it is telling me that I am receiving inferring latches. Could I get some help on what the issue could be? (line 76-78 is inside of the SIDLE state by the way)

Thanks in advance!

Error Message:

module code:

addition: These are all the synthesis error messages, in case there's a related error message

[IP_Flow 19-3571] IP 'design_1_Debounce_Switch_0_0' is restricted:

* Module reference is stale and needs refreshing.

[Synth 8-589] replacing case/wildcard equality operator !== with logical equality operator != ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/imports/Downloads/Debounce_Switch.v":19]

[Common 17-576] 'use_project_ipc' is deprecated. This option is deprecated and no longer used.

[Constraints 18-5210] No constraints selected for write.

Resolution: This message can indicate that there are no constraints for the design, or it can indicate that the used_in flags are set such that the constraints are ignored. This later case is used when running synth_design to not write synthesis constraints to the resulting checkpoint. Instead, project constraints are read when the synthesized design is opened.

design_1_uart_top_0_0_synth_1[IP_Flow 19-3571] IP 'design_1_uart_top_0_0' is restricted:

* Module reference is stale and needs refreshing.

[Synth 8-327] inferring latch for variable 'FSM_sequential_wNextState_reg' ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/new/uart_receiver.v":76]

[Synth 8-327] inferring latch for variable 'FSM_onehot_wNextState_reg' ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/new/uart_receiver.v":76]

[Synth 8-327] inferring latch for variable 'FSM_onehot_wNextState_reg' ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/new/uart_receiver.v":76]

[Synth 8-327] inferring latch for variable 'wBufferNext_reg' ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/new/uart_receiver.v":79]

[Synth 8-327] inferring latch for variable 'wCntClockNext_reg' ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/new/uart_receiver.v":78]

[Synth 8-327] inferring latch for variable 'wBitCountNext_reg' ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/new/uart_receiver.v":77]

[Common 17-576] 'use_project_ipc' is deprecated. This option is deprecated and no longer used.

[Constraints 18-5210] No constraints selected for write.

Resolution: This message can indicate that there are no constraints for the design, or it can indicate that the used_in flags are set such that the constraints are ignored. This later case is used when running synth_design to not write synthesis constraints to the resulting checkpoint. Instead, project constraints are read when the synthesized design is opened.

I was wondering if I could get some help on the following issue.

I am getting latches for the registers shown in the picture and I can't figurer out why that is the case. It is a uart_rx module with an FSM. When determining the next state logic it is telling me that I am receiving inferring latches. Could I get some help on what the issue could be? (line 76-78 is inside of the SIDLE state by the way)

Thanks in advance!

Error Message:

module code:

Code:

`timescale 1ns / 1ps

module uart_receiver #(

parameter CLK_FREQ = 125_000_000,

parameter BAUD_RATE = 115_200,

// Example: 125 MHz Clock / 115200 baud UART -> CLKS_PER_BIT = 1085

parameter CLKS_PER_BIT = CLK_FREQ / BAUD_RATE

)

(

input wire iClk, iRst,

input wire iRxSerial,

output wire [7:0] oRxByte,

output wire oRxDone

);

// states (5)

localparam SIDLE = 3'b000;

localparam RXSTART = 3'b001;

localparam RXDATA = 3'b010;

localparam RXSAMPLE = 3'b011;

localparam RXSTOP = 3'b100;

localparam SDONE = 3'b101;

//4: registers + state register

reg[2:0] rBitCountCurrent, wBitCountNext;

reg rDataCurrent1, rDataCurrent2;

reg [2:0] rCurrentState, wNextState;

reg [$clog2(CLKS_PER_BIT - 1): 0] rCntClockCurrent, wCntClockNext;

reg [7:0] rBufferCurrent, wBufferNext;

always @(posedge iClk) begin

// double reg to for metastability issue.

rDataCurrent1 <= iRxSerial;

rDataCurrent2 <= rDataCurrent1;

if (iRst) begin

rBitCountCurrent <= 0;

rCurrentState <= SIDLE;

rCntClockCurrent <= 0;

rBufferCurrent <=0 ;

end

else begin

rBitCountCurrent <= wBitCountNext;

rCurrentState <= wNextState;

rCntClockCurrent <= wCntClockNext;

rBufferCurrent <=wBufferNext;

end

end

// next state logic

// next state logic

always @(*) begin

case (rCurrentState)

SIDLE: begin

if (rDataCurrent2 == 0) begin

wNextState = RXSTART;

wBitCountNext = 0;

wCntClockNext = 0;

wBufferNext = 0;

end

else begin

wNextState = SIDLE;

wBitCountNext = 0;

wCntClockNext = 0;

wBufferNext = 0;

end

end

RXSTART: begin

wBufferNext = rBufferCurrent;

wBitCountNext = 0;

if (rCntClockCurrent == CLKS_PER_BIT - 3) begin

wNextState = RXDATA;

wCntClockNext = 0;

end

else begin

wNextState = RXSTART;

wCntClockNext = rCntClockCurrent + 1;

end

end

RXDATA: begin

if (rCntClockCurrent == (CLKS_PER_BIT - 1) /2 ) begin // sample data

wNextState = RXSAMPLE;

wCntClockNext = rCntClockCurrent + 1;

wBitCountNext = rBitCountCurrent;

wBufferNext = rBufferCurrent;

end

else if (

rCntClockCurrent == CLKS_PER_BIT - 1 && rBitCountCurrent == 7

) begin // byte transferred

wNextState = RXSTOP;

wCntClockNext = 0;

wBitCountNext = rBitCountCurrent; // should it be incremented? not sure!

wBufferNext = rBufferCurrent;

end

else if (

rCntClockCurrent == CLKS_PER_BIT - 1

) begin // cycles per bit reached

wNextState <= RXDATA;

wBitCountNext <= rBitCountCurrent + 1;

wCntClockNext <= 0;

wBufferNext = rBufferCurrent;

end

else begin // just counting, no case reached.

wNextState <= RXDATA;

wBitCountNext <= rBitCountCurrent;

wCntClockNext <= rCntClockCurrent + 1;

wBufferNext = rBufferCurrent;

end

end

RXSAMPLE: begin

wCntClockNext <= rCntClockCurrent + 1;

wBitCountNext <= rBitCountCurrent;

wNextState <= RXDATA;

wBufferNext <= {rDataCurrent2, rBufferCurrent[7:1]}; // LSB is at end (right most side)

end

RXSTOP: begin

wBitCountNext <= rBitCountCurrent;

wBufferNext <= rBufferCurrent;

if (rCntClockCurrent == CLKS_PER_BIT - 1) begin

wNextState <= SDONE;

wCntClockNext <= rCntClockCurrent;

end

else begin

wNextState <= RXSTOP;

wCntClockNext <= rCntClockCurrent + 1;

end

end

SDONE: begin

wBitCountNext <= 0;

wCntClockNext <= 0;

wBufferNext <= rBufferCurrent;

wNextState <= SIDLE;

end

default: begin

wBitCountNext <= 0;

wCntClockNext <= 0;

wBufferNext <= rBufferCurrent;

wNextState <= SIDLE;

end

endcase

end

// output logic

assign oRxByte = rDataCurrent2;

assign oRxDone = (rCurrentState == SDONE) ? 1 : 0;

endmodule

--- Updated ---

addition: These are all the synthesis error messages, in case there's a related error message

[IP_Flow 19-3571] IP 'design_1_Debounce_Switch_0_0' is restricted:

* Module reference is stale and needs refreshing.

[Synth 8-589] replacing case/wildcard equality operator !== with logical equality operator != ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/imports/Downloads/Debounce_Switch.v":19]

[Common 17-576] 'use_project_ipc' is deprecated. This option is deprecated and no longer used.

[Constraints 18-5210] No constraints selected for write.

Resolution: This message can indicate that there are no constraints for the design, or it can indicate that the used_in flags are set such that the constraints are ignored. This later case is used when running synth_design to not write synthesis constraints to the resulting checkpoint. Instead, project constraints are read when the synthesized design is opened.

design_1_uart_top_0_0_synth_1[IP_Flow 19-3571] IP 'design_1_uart_top_0_0' is restricted:

* Module reference is stale and needs refreshing.

[Synth 8-327] inferring latch for variable 'FSM_sequential_wNextState_reg' ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/new/uart_receiver.v":76]

[Synth 8-327] inferring latch for variable 'FSM_onehot_wNextState_reg' ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/new/uart_receiver.v":76]

[Synth 8-327] inferring latch for variable 'FSM_onehot_wNextState_reg' ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/new/uart_receiver.v":76]

[Synth 8-327] inferring latch for variable 'wBufferNext_reg' ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/new/uart_receiver.v":79]

[Synth 8-327] inferring latch for variable 'wCntClockNext_reg' ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/new/uart_receiver.v":78]

[Synth 8-327] inferring latch for variable 'wBitCountNext_reg' ["/home/sims0702/cdd_lab_2/cdd_lab_2.srcs/sources_1/new/uart_receiver.v":77]

[Common 17-576] 'use_project_ipc' is deprecated. This option is deprecated and no longer used.

[Constraints 18-5210] No constraints selected for write.

Resolution: This message can indicate that there are no constraints for the design, or it can indicate that the used_in flags are set such that the constraints are ignored. This later case is used when running synth_design to not write synthesis constraints to the resulting checkpoint. Instead, project constraints are read when the synthesized design is opened.

Last edited: