hosseineslahi7

Junior Member level 1

Dear experts,

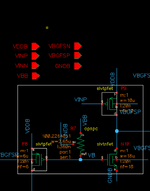

I have designed a simple design working as a level-shifter and buffer at 1GHz in GF22nm technology. Then, my colleague and I designed two roughly similar layouts for my design, however, we see completely different post-layout results. We carefully connected the back-gates, DEEP NWELL layers, substrate, gnd and VDD to the correct biases on both layouts. The floorplans are also similar with minor changes in the wiring routs only. So, we could not understand what is going on.

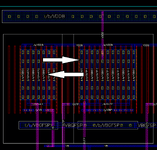

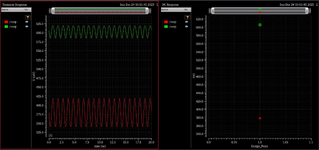

Then I realized that if I change the location of only two PMOS devices (P9 and P8 on schematic) in my layout, as I showed in figures 1 and Figure 2, posy-layout results will change dramatically. You can see the difference in figure 3. It means a small change in layout will shift the result.

Does anyone know how it is possible? Is it because of my design or something is wrong in PDK?

I have designed a simple design working as a level-shifter and buffer at 1GHz in GF22nm technology. Then, my colleague and I designed two roughly similar layouts for my design, however, we see completely different post-layout results. We carefully connected the back-gates, DEEP NWELL layers, substrate, gnd and VDD to the correct biases on both layouts. The floorplans are also similar with minor changes in the wiring routs only. So, we could not understand what is going on.

Then I realized that if I change the location of only two PMOS devices (P9 and P8 on schematic) in my layout, as I showed in figures 1 and Figure 2, posy-layout results will change dramatically. You can see the difference in figure 3. It means a small change in layout will shift the result.

Does anyone know how it is possible? Is it because of my design or something is wrong in PDK?