promach

Advanced Member level 4

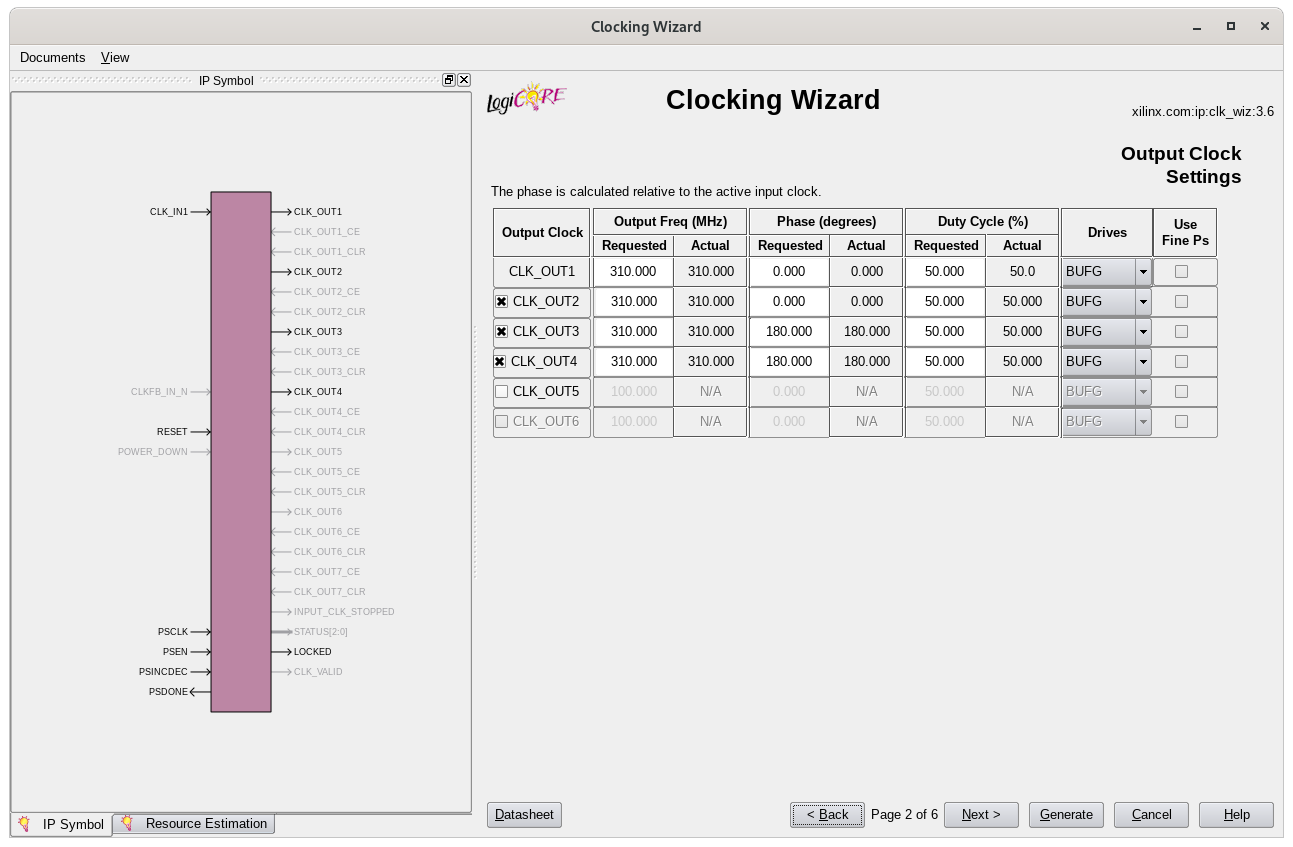

As for PLL dynamic phase shift approach, I have few questions:

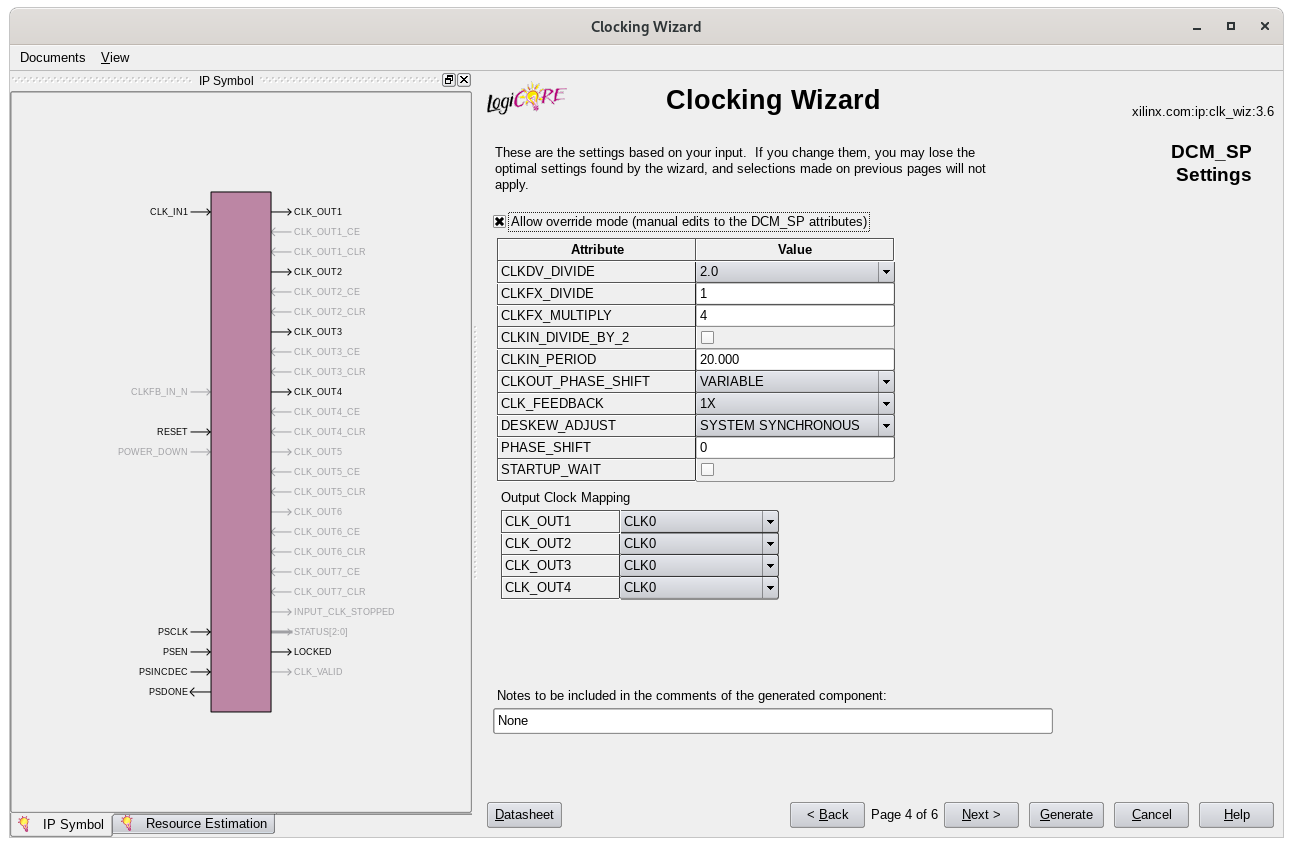

1. Could I actually generate a 90 degree phase-shifted clock from CLK_OUT2 using DCM_SP Settings ?

Could I actually generate a 270 degree phase shifted clock from CLK_OUT4 using DCM_SP Settings ?

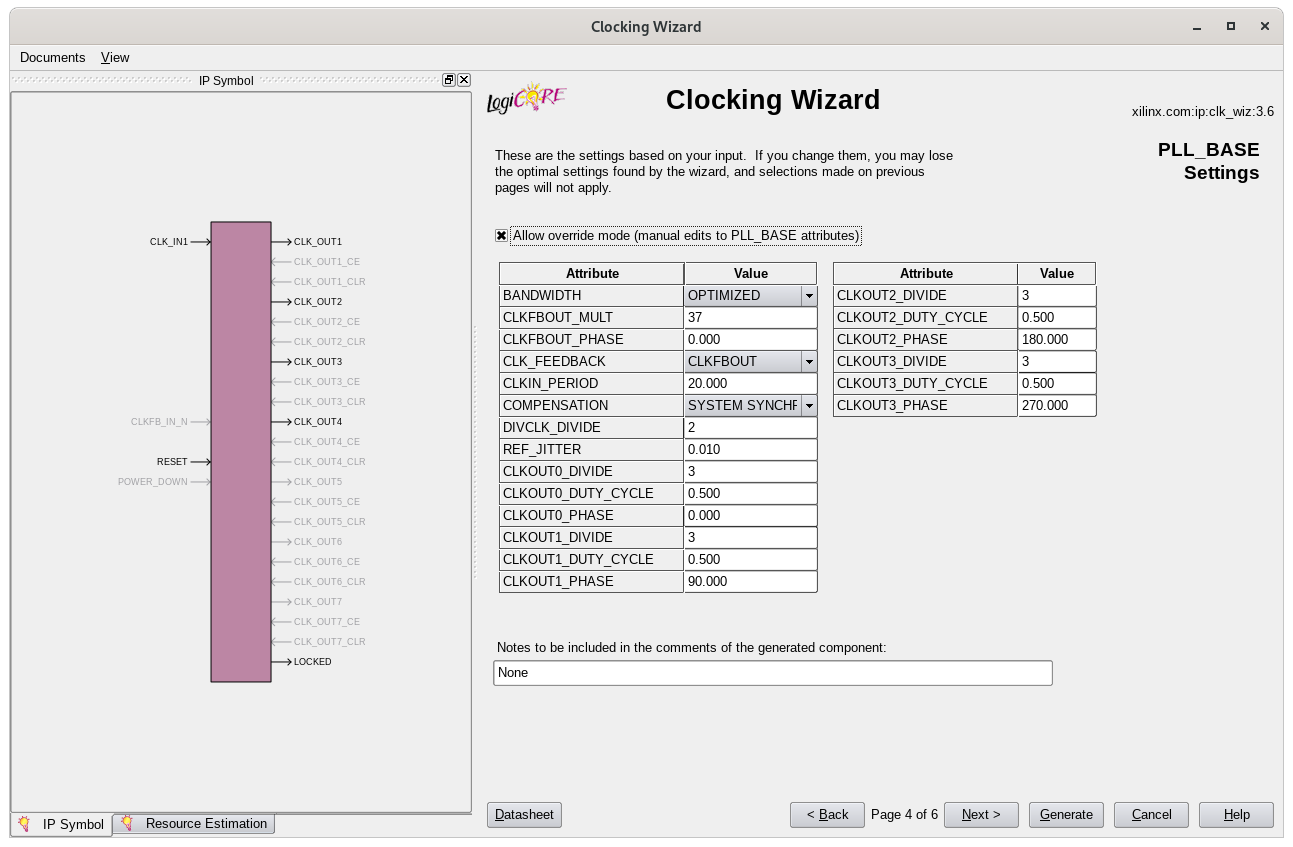

2. What about PLL_BASE Settings which seems to have the phase shift capability as well ?

1. Could I actually generate a 90 degree phase-shifted clock from CLK_OUT2 using DCM_SP Settings ?

Could I actually generate a 270 degree phase shifted clock from CLK_OUT4 using DCM_SP Settings ?

2. What about PLL_BASE Settings which seems to have the phase shift capability as well ?