ljp2706

Advanced Member level 4

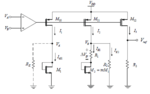

LVT devices will have a larger leakage current due to reduced control of the channel. But since you have a voltage supply of 1V for the amplifier you could probably use standard devices. To get more gain out of the second stage you could self-cascode the output structure. Or you could increase the transconductance of the differential input.

You don't really need to switch to standard VT devices just so you know. Even though the LVTs have more leakage current, just set the quiescent currents in your amplifier to meet your specifications. One thing to keep in mind is that LVTs usually cost extra to fabricate since its not the standard.

You don't really need to switch to standard VT devices just so you know. Even though the LVTs have more leakage current, just set the quiescent currents in your amplifier to meet your specifications. One thing to keep in mind is that LVTs usually cost extra to fabricate since its not the standard.