Alipoursaadaty

Member level 3

Hello,

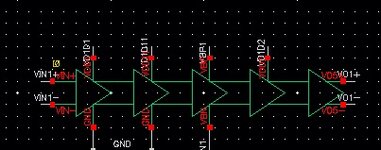

I am an IC designer and have designed open-loop amplifiers with about 80 dB voltage gain and 200 MHz bandwidth. The structure of the amplifiers is a 4-stage 20 dB amplifier with a buffer at the output (it is a 5-stage with a buffer). As I designed this amplifier in open-loop mode, I expected to prevent instability and oscillation. However, I am now measuring the fabricated chip in 65 nm TSMC tech. Would you please let me know if the grounding and VDD loops cause this oscillation? I connected all the grounds of each stage in the layout. However, the VDD of the first stage and buffer are unique and are separated from the second, third, and fourth stages. The voltage bias of the transistors is generated by the bias method and common-mode feedback circuits. Self-bias loop gains are so small and cannot create oscillation.

In the measuring, I can tune the voltage bias of some transistors to control the gain. By reducing the voltage gain to 40, 50, and in some cases 60 dB, oscillation is going to be suppressed. Also, the oscillation frequencies are almost higher than 100 MHz to 2 GHz. However, most of them are near the 1 GHz.

During the post-layout simulation, there was no oscillation in these amplifiers. How can I model this oscillation in the Cadence? In other words, why was not the oscillation seen in the post-layout simulations?

Is there anyone to help me to find out the main problem?

Regards,

I am an IC designer and have designed open-loop amplifiers with about 80 dB voltage gain and 200 MHz bandwidth. The structure of the amplifiers is a 4-stage 20 dB amplifier with a buffer at the output (it is a 5-stage with a buffer). As I designed this amplifier in open-loop mode, I expected to prevent instability and oscillation. However, I am now measuring the fabricated chip in 65 nm TSMC tech. Would you please let me know if the grounding and VDD loops cause this oscillation? I connected all the grounds of each stage in the layout. However, the VDD of the first stage and buffer are unique and are separated from the second, third, and fourth stages. The voltage bias of the transistors is generated by the bias method and common-mode feedback circuits. Self-bias loop gains are so small and cannot create oscillation.

In the measuring, I can tune the voltage bias of some transistors to control the gain. By reducing the voltage gain to 40, 50, and in some cases 60 dB, oscillation is going to be suppressed. Also, the oscillation frequencies are almost higher than 100 MHz to 2 GHz. However, most of them are near the 1 GHz.

During the post-layout simulation, there was no oscillation in these amplifiers. How can I model this oscillation in the Cadence? In other words, why was not the oscillation seen in the post-layout simulations?

Is there anyone to help me to find out the main problem?

Regards,