pgib8

Member level 2

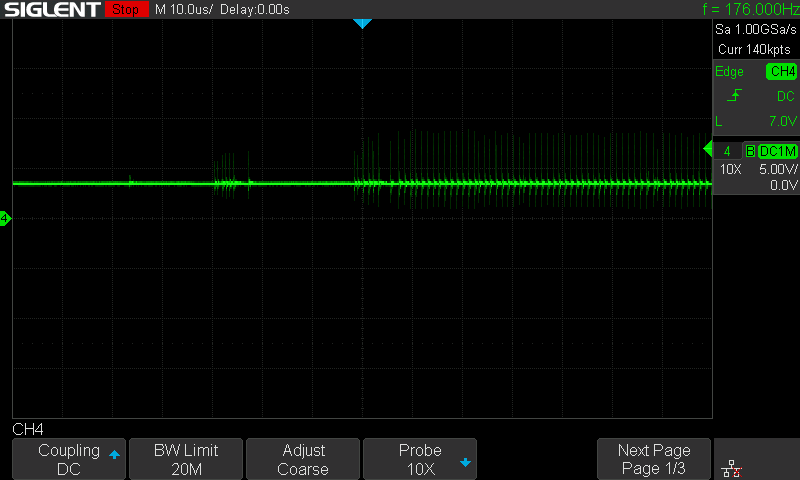

Hi, I'm getting a voltage spike from a power supply and I'm measuring it directly at the microcontroller (MCU). I know that it exceeds the absolute maximum rating but it is extremely bief. You can see below that it is about 10 V and the absolute maximum rating for the MCU is 4 V, however it appears to only last for maybe 20 ns. When it comes to damage all I know is that it is the heat that causes the damage, so because of how short it is, it will not be enough energy to do this. What I don't know is if even a very short pulse like this can cause damage. Also it is not only 1 spike but there are a lot of them. Of course if it was me, I would have seen to it that this gets filtered out for good measure but the source of this is done by another person. I have to decide for myself if I tell them that this needs to be fixed or if this is completely normal and/or should be ignored. See scope shots below.

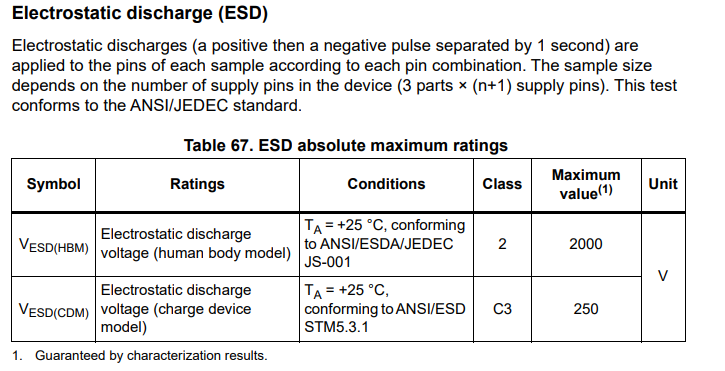

The only thing that tells me that it is OK is the following from the datasheet:

Does that mean that I can ignore these spikes? If yes, then I have to check the same for every other IC on the board that is exposed to this for the same?

The only thing that tells me that it is OK is the following from the datasheet:

Does that mean that I can ignore these spikes? If yes, then I have to check the same for every other IC on the board that is exposed to this for the same?