coshy

Member level 4

Dear All,

I'm trying to resolve current timing violation in back annotation with post gate netlist simulation.

Our third party Back-End company progressed STA and made SDF.

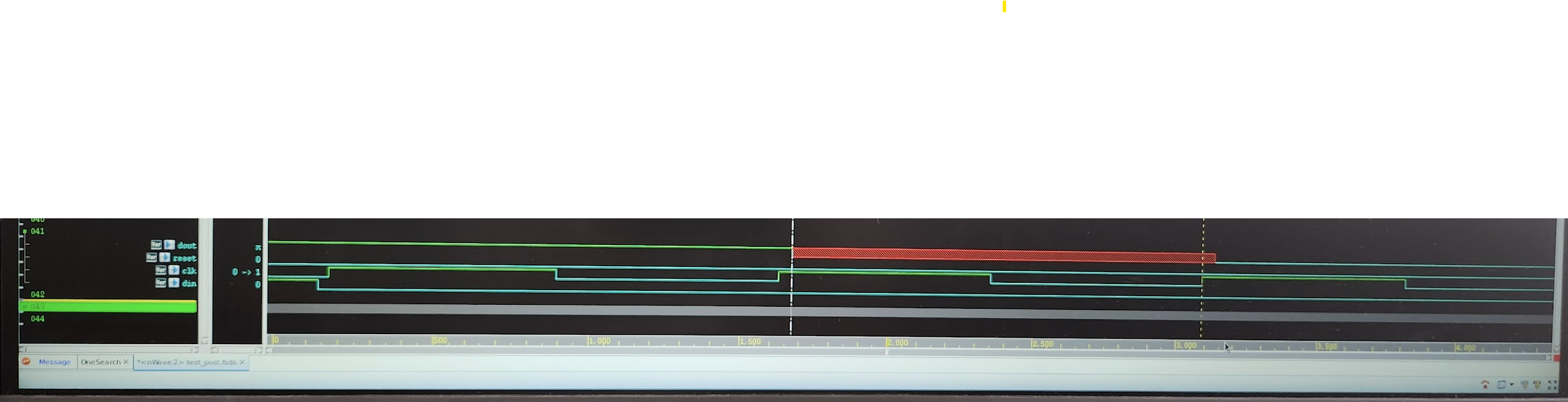

As you can see the below, that is the simple SDFF register. Inputs are clk, din, reset and output is dout.

Here is I can't understand because there is no reason for unknow value of dout. why suddenly dout makes the unknow value?

If this Timing Violation is valid, What thing should I have to check to resolve?

I'm trying to resolve current timing violation in back annotation with post gate netlist simulation.

Our third party Back-End company progressed STA and made SDF.

As you can see the below, that is the simple SDFF register. Inputs are clk, din, reset and output is dout.

Here is I can't understand because there is no reason for unknow value of dout. why suddenly dout makes the unknow value?

If this Timing Violation is valid, What thing should I have to check to resolve?