nadd

Member level 1

Hi everyone,

I'm very new to designing a circuit. So, I need some help.

I need to design an ADC for an external, sampled, single-ended signal. The frequency is 1 Mhz, and desired speed is at least 4msps and the resolution is at least 14 bits.

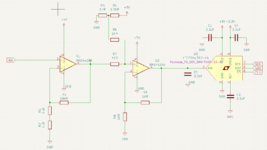

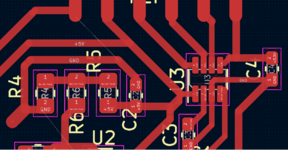

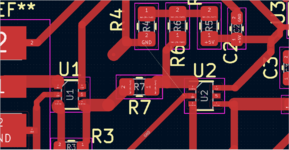

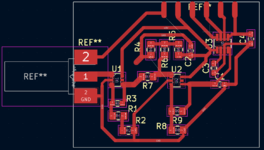

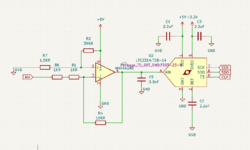

I checked ADC chips and found LTC2314-14 to use. But, LTC2314-14 has inputs for S/H, and my input signal is already sampled. Would it be a problem? (LTC2314-14 Datasheet: https://www.mouser.com/datasheet/2/609/231414fa-2954440.pdf )

Also, I found ADS1605, this one has differential input, so will I need a single-ended to differential converter? (ADS1605 Datasheet: https://www.ti.com/lit/ds/symlink/ads1605.pdf?ts=1664705456913 )

If there are any different ADC chips that you would recommend, please let me know. (Preferably, easy to solder). Also, which additional components should I use in my design?

Thanks in advance!

I'm very new to designing a circuit. So, I need some help.

I need to design an ADC for an external, sampled, single-ended signal. The frequency is 1 Mhz, and desired speed is at least 4msps and the resolution is at least 14 bits.

I checked ADC chips and found LTC2314-14 to use. But, LTC2314-14 has inputs for S/H, and my input signal is already sampled. Would it be a problem? (LTC2314-14 Datasheet: https://www.mouser.com/datasheet/2/609/231414fa-2954440.pdf )

Also, I found ADS1605, this one has differential input, so will I need a single-ended to differential converter? (ADS1605 Datasheet: https://www.ti.com/lit/ds/symlink/ads1605.pdf?ts=1664705456913 )

If there are any different ADC chips that you would recommend, please let me know. (Preferably, easy to solder). Also, which additional components should I use in my design?

Thanks in advance!