amitjagtap

Full Member level 5

hi all,

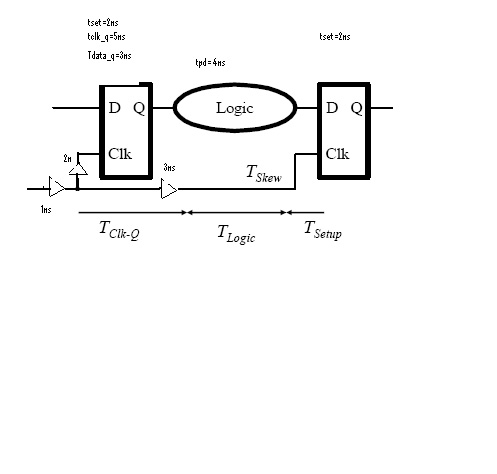

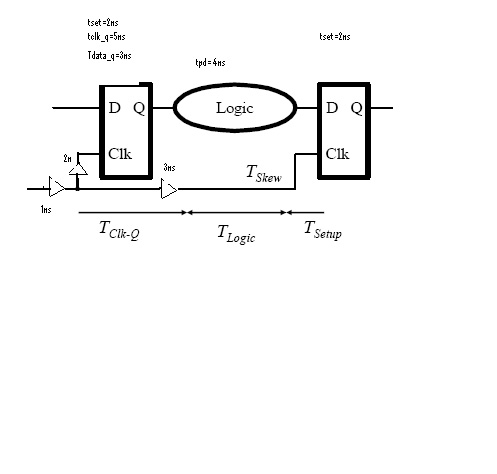

In the fig below how to cal fmax.

what will be the skew here.

Is there any use of Tdata_q.if yes what it is?

thanking you,

Amit

In the fig below how to cal fmax.

what will be the skew here.

Is there any use of Tdata_q.if yes what it is?

thanking you,

Amit