unixdaemon

Newbie level 6

I've ran the Fusion Compiler on a simple module:

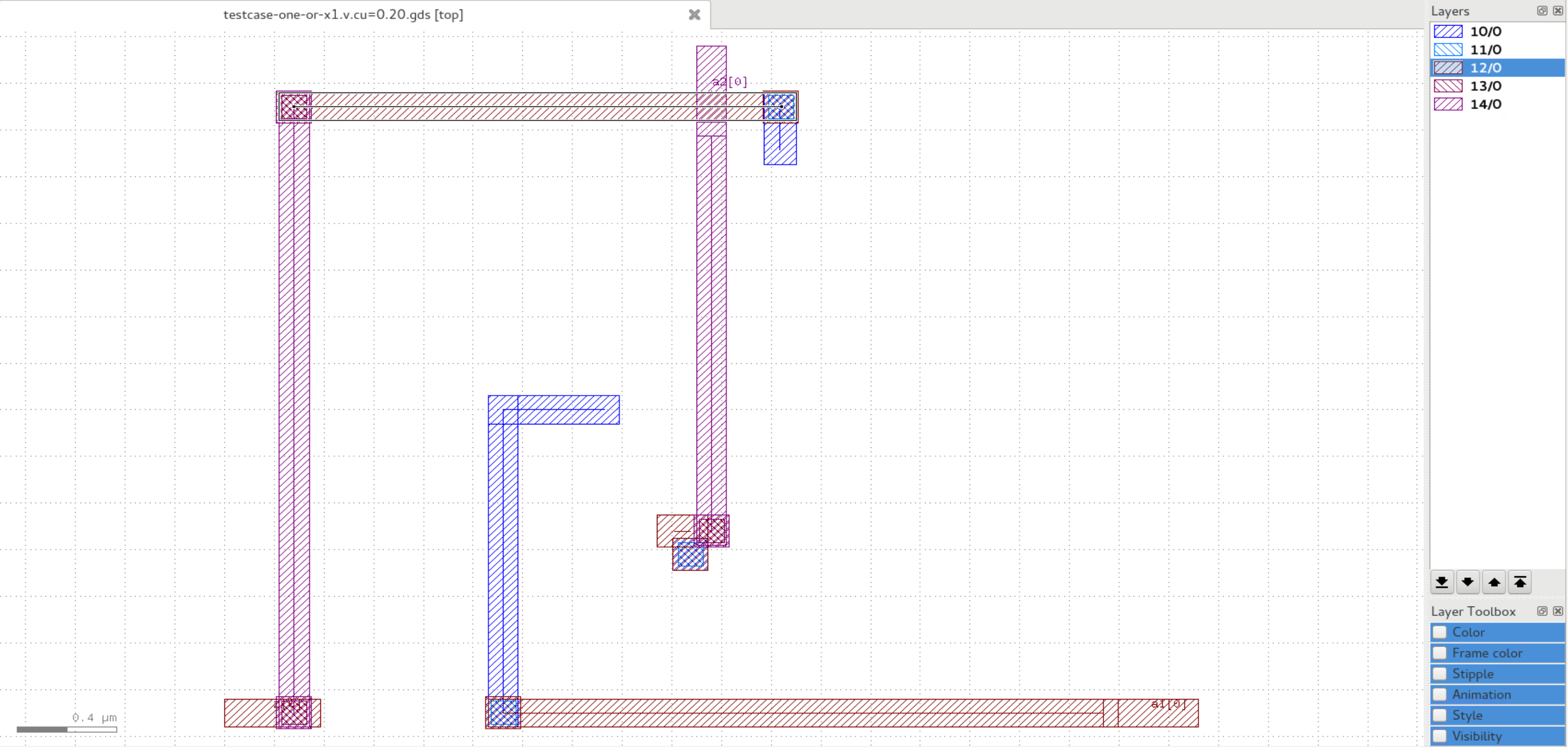

Fusion Compiler generated the GDS file that KLayout shows like this:

I have trouble relating the original Verilog code with this GDS image.

How can one understand that there is a single logical-OR gate present here?

Where are the transistors?

Shouldn't the material come close to each other to form NPN or PNP transistors?

And where are VSS and VDD lines? Shouldn't they be always present?

It looks to me that a1[0], a2[0] and z[0] are all disconnected from each other as shown on the above picture.

Larger designs result in more layers in the GDS file.

How to understand what these layers represent since the GDS viewer only shows them as numbers NN/0?

What to read in order to understand the ASIC's GDS structure better?

Code:

module top(a1, a2, z);

input [0:0] a1;

input [0:0] a2;

output [0:0] z;

assign z = a1 | a2;

endmoduleFusion Compiler generated the GDS file that KLayout shows like this:

I have trouble relating the original Verilog code with this GDS image.

How can one understand that there is a single logical-OR gate present here?

Where are the transistors?

Shouldn't the material come close to each other to form NPN or PNP transistors?

And where are VSS and VDD lines? Shouldn't they be always present?

It looks to me that a1[0], a2[0] and z[0] are all disconnected from each other as shown on the above picture.

Larger designs result in more layers in the GDS file.

How to understand what these layers represent since the GDS viewer only shows them as numbers NN/0?

What to read in order to understand the ASIC's GDS structure better?

Last edited: