bsrin

Junior Member level 3

Hi Everyone,

I worked on ESD layouts in Wirebond option IP where VDD/VSS is connected to internal circuit through ESD cell.

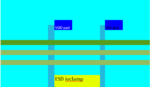

Now , I am working on Bump option IP. My doubt is whether I need to connect the VDD/VSS bump to the IP power mesh through ESD circuit which is 400um wide from esd circuit. With this, VDD to ESD and to IP power mesh will be huge which again creates an IR Drop issue.

Can somebody suggest me how they have connected the bump VDD/VSS to Internal PowerSupply Mesh.

Can we connect bump VDD/VSS(bump placement is nearly middle of IP) to Internal power mesh directly which also connects to ESD block which is sitting bottom of the IP.

Thanks in Advance,

bsrin

I worked on ESD layouts in Wirebond option IP where VDD/VSS is connected to internal circuit through ESD cell.

Now , I am working on Bump option IP. My doubt is whether I need to connect the VDD/VSS bump to the IP power mesh through ESD circuit which is 400um wide from esd circuit. With this, VDD to ESD and to IP power mesh will be huge which again creates an IR Drop issue.

Can somebody suggest me how they have connected the bump VDD/VSS to Internal PowerSupply Mesh.

Can we connect bump VDD/VSS(bump placement is nearly middle of IP) to Internal power mesh directly which also connects to ESD block which is sitting bottom of the IP.

Thanks in Advance,

bsrin