Jordon

Member level 1

- Joined

- Dec 25, 2022

- Messages

- 33

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 6

- Location

- Shanghai, China

- Activity points

- 265

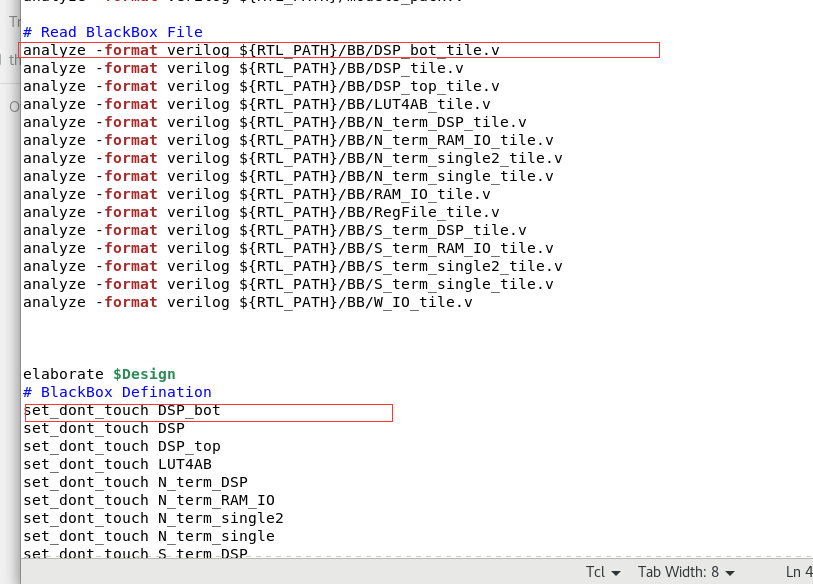

Hi, i am tring to add a blackbox into a topdesign.

I have pass RTL2GDSII flow in innovus for the module, and save all the output files. And then, i need to to add the module into topdesign, synthesys in Design Compiler, So i add a command set_dont touch XXX after read verilog, like the figure below,

However, the command 'set_dont_touch' seems not works, because DC still report unresolved references, is there some steps was wrong?

Another question, how to add the blackbox timing information from the files created by innovus? I think maybe some .lib? But i dont find something with .lib in innovus output files. Maybe i need to change the way to post the second question, what files are needed from innovus and how to add them?

Many thanks!!

I have pass RTL2GDSII flow in innovus for the module, and save all the output files. And then, i need to to add the module into topdesign, synthesys in Design Compiler, So i add a command set_dont touch XXX after read verilog, like the figure below,

However, the command 'set_dont_touch' seems not works, because DC still report unresolved references, is there some steps was wrong?

Another question, how to add the blackbox timing information from the files created by innovus? I think maybe some .lib? But i dont find something with .lib in innovus output files. Maybe i need to change the way to post the second question, what files are needed from innovus and how to add them?

Many thanks!!