Jordon

Member level 1

- Joined

- Dec 25, 2022

- Messages

- 33

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 6

- Location

- Shanghai, China

- Activity points

- 262

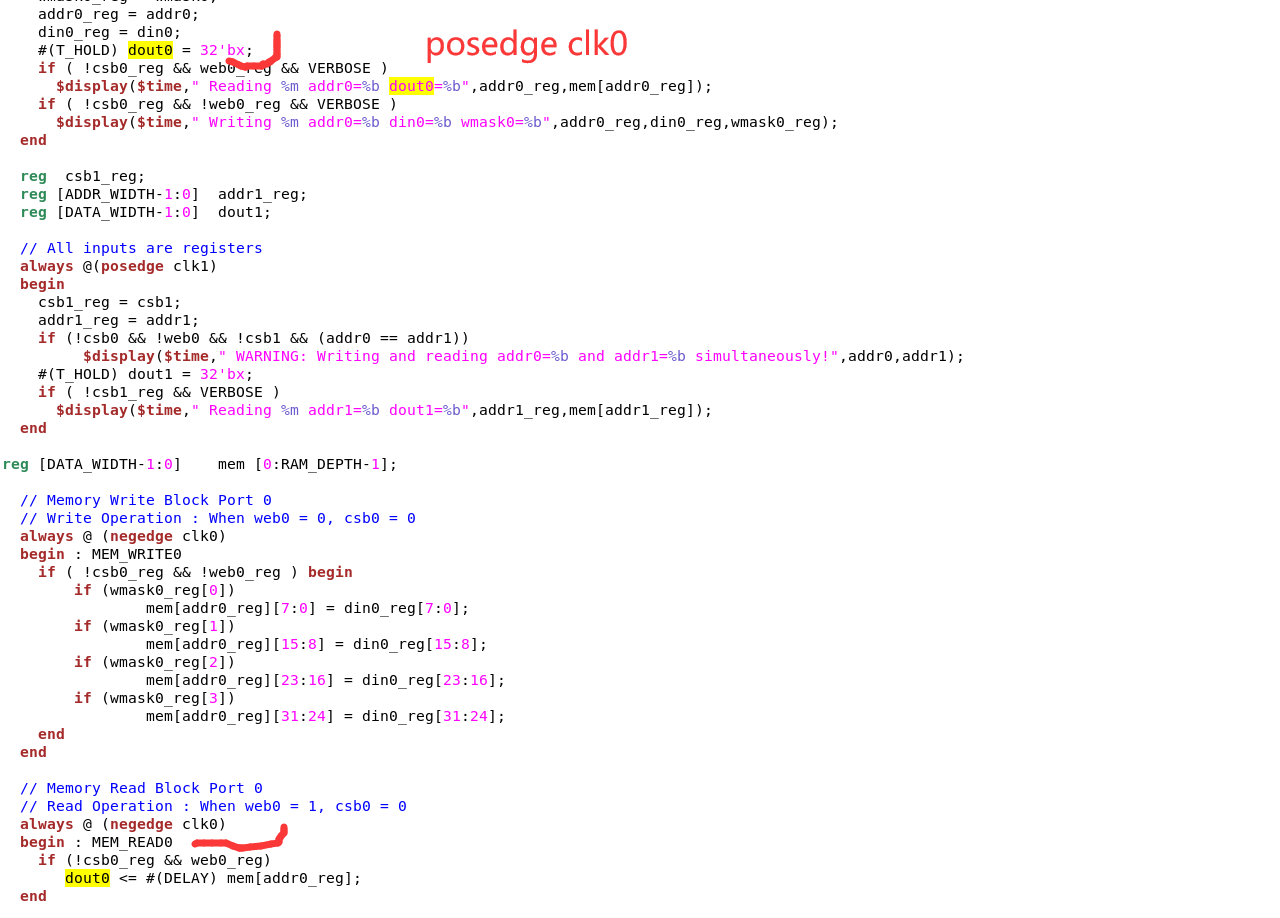

hi, i am tring to compile a sram module from sky company, but the RTL codes has two clk(i dont know how to describe this situation), like the picture below, it has both posedge and negedge clk's always block,

i compile as normal, same as the design with one clk edge, but it seems the tools think it has one edge clk:

![L4]J2ZOHBR$5V]D_]_~}BFG.png L4]J2ZOHBR$5V]D_]_~}BFG.png](https://www.edaboard.com/attachments/l4-j2zohbr-5v-d_-_-bfg-png.181037/)

how can i change the command or what should I add in the tcl?

i compile as normal, same as the design with one clk edge, but it seems the tools think it has one edge clk:

how can i change the command or what should I add in the tcl?