quocviet19501

Newbie level 6

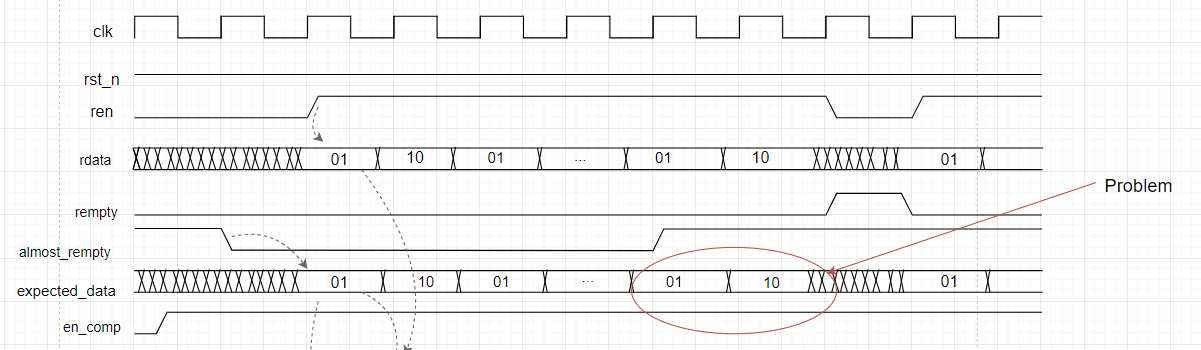

Hi all, thank you for reading my post. I need to design a comparator, because of FIFO problem I have to use the almost_rempty signal to read the data from 1 block (gen block) and signal ren to read data from FIFO block. In the picture below, you can see that when reading the expected_data from gen block it misses 2 final data since the almost_rempty is faster than rempty (assert when FIFO is empty) signal 2 clk cycles. Can anyone suggest a solution?