liteon

Full Member level 2

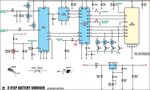

Hi, I need to build a charger for high capacity lead acid battery.It is a three stage battery charger for both low and high capacity batteries.Seem good choice to me,So i checked the market before starting the project and found almost all components except A/D converter TLC548,i can get ADC0831 which is same package (8-pin Dip).But it not pin compatible which is not a bigger problem.The circuit is controlled by a PIC chip , a 2-ch analogue multiplexer-demultiplexer performs monitoring of battery status and feeds it to A/D converter and data is received by the PIC chip.

Can i use the ADC0831 in place of TLC548.

Do i need to re-write the code for PIC in case i use ADC0831?

Can i use the ADC0831 in place of TLC548.

Do i need to re-write the code for PIC in case i use ADC0831?