AMSA84

Advanced Member level 2

- Joined

- Aug 24, 2010

- Messages

- 577

- Helped

- 8

- Reputation

- 16

- Reaction score

- 8

- Trophy points

- 1,298

- Location

- Iberian Peninsula

- Activity points

- 6,178

Hi guys,

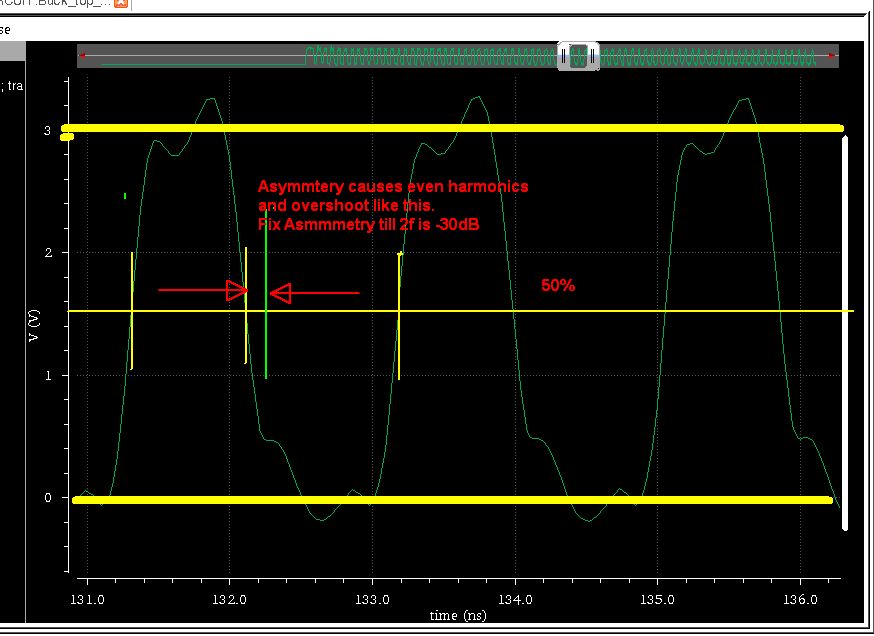

I am using a chain of inverters to drive a power mosfet. Those drivers must process the driving signal at very high frequency.

One problem that I am facing is that the signal at the output of each of the inverters have a large peak, looking like an inverter hyperbola with that peak voltage reaching the house of 3.7V.

Does anyone knows what might be causing this?

I am using a chain of inverters to drive a power mosfet. Those drivers must process the driving signal at very high frequency.

One problem that I am facing is that the signal at the output of each of the inverters have a large peak, looking like an inverter hyperbola with that peak voltage reaching the house of 3.7V.

Does anyone knows what might be causing this?