dshoter13

Member level 4

- Joined

- Oct 20, 2014

- Messages

- 72

- Helped

- 4

- Reputation

- 8

- Reaction score

- 4

- Trophy points

- 8

- Activity points

- 619

RF CMOS Power Amplifier Design - Virtuoso

Hi. I'm trying to design a CMOS Class B PA using Virtuoso. I designed my output matching network for maximum gain.. but when I'm simulating S-Param, Harmonic Balance and doing Periodic States Simulations etc, I have to use a Port, and It comes with 50Ohm resistence. My question is: it will have impact in my PA performance? Do I have to design a input matching network to obtain the correct results in Virtuoso?

Thank you all for you attention.

Best regards.

- - - Updated - - -

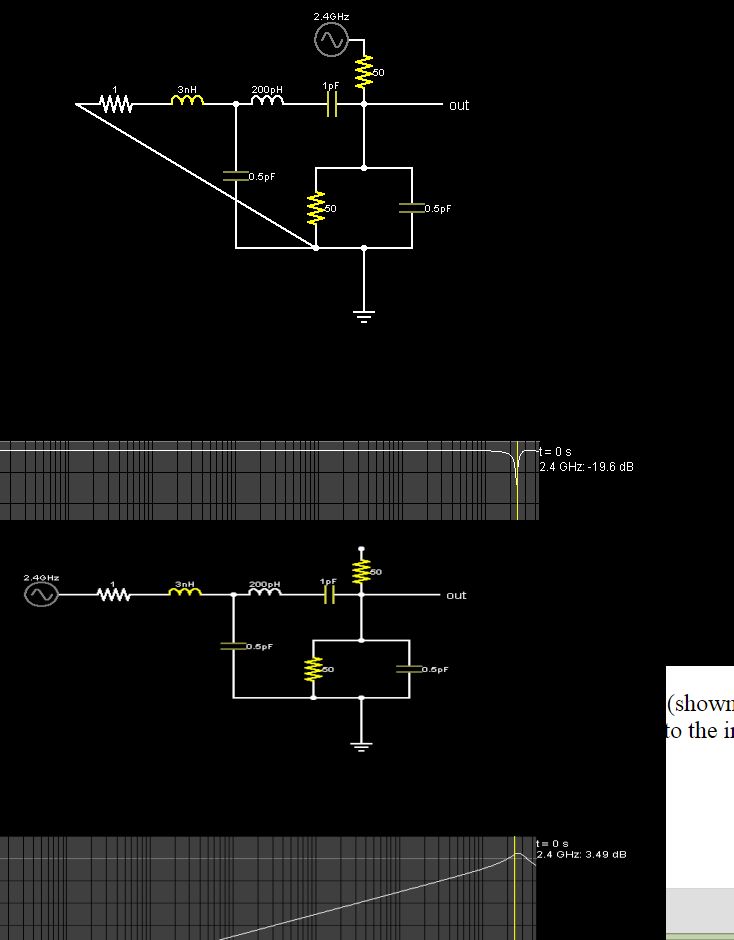

Sorry, I design a very simple low-pass matching network (ideal elements) and it boosted the PAE and Output Power.

Thank you all for you attention.

Hi. I'm trying to design a CMOS Class B PA using Virtuoso. I designed my output matching network for maximum gain.. but when I'm simulating S-Param, Harmonic Balance and doing Periodic States Simulations etc, I have to use a Port, and It comes with 50Ohm resistence. My question is: it will have impact in my PA performance? Do I have to design a input matching network to obtain the correct results in Virtuoso?

Thank you all for you attention.

Best regards.

- - - Updated - - -

Sorry, I design a very simple low-pass matching network (ideal elements) and it boosted the PAE and Output Power.

Thank you all for you attention.