wandola

Junior Member level 3

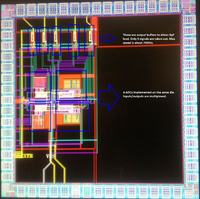

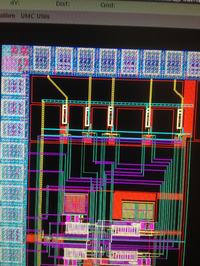

I have designed a SAR-ADC. I am doing some testing now.

I build the testing circuits. I have encountered some very funny issues which cannot be explained explicitly.

I have attached a ppt slides I sent to my boss.

The problem is that, when the output pad is loaded with something (just a wire), the ground signal becomes noisy. As a results, my other signals are all noisy, including input signals to my ADC, reference voltages, even the power supply.

--

The ADC output was designed to drive 8-pF capacitance. With the consideration of layout and parasitics, it should be able to drive at least 5pF. However, whenever the output is loaded with something, all other signals are distorted.

I don't know whether it is my ADC layout problem or the PCB problem.

I build the testing circuits. I have encountered some very funny issues which cannot be explained explicitly.

I have attached a ppt slides I sent to my boss.

The problem is that, when the output pad is loaded with something (just a wire), the ground signal becomes noisy. As a results, my other signals are all noisy, including input signals to my ADC, reference voltages, even the power supply.

--

The ADC output was designed to drive 8-pF capacitance. With the consideration of layout and parasitics, it should be able to drive at least 5pF. However, whenever the output is loaded with something, all other signals are distorted.

I don't know whether it is my ADC layout problem or the PCB problem.