wjxcom

Full Member level 5

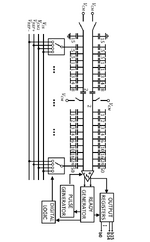

Hi all: look at this interesting sar topology, which still uses redundancy technology and uses Main-Sub-DAC Array. In this capacitor array, the highest and second highest bits are "taken" from 22 unit capacitors, but only 11 unit capacitors are used in the high position capacitor array, and the rest may be placed in the LSB capacitor array, but there are only 4 (or 3?) redundancy in the LSB array instead of 11. I don't understand, how do you put redundancy in the MSB array into the LSB array? This topology comes from Low-Power High-Performance SAR ADC with Redundancy and Digital Background Calibration,the author is Albert Hsu Ting Chang

Please help me, thax!!!

Please help me, thax!!!