sun_ray

Advanced Member level 3

Can we use this following in Verilog

y= ( a | ~b) where a and b are inputs and y is an output?

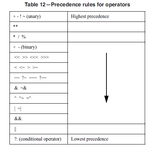

The reason I ask this question because we are using parantheses () here and in Verilog specification file I am not able to find where () is defined. In the list of operator I do not find () is defined. Is it an allowed construct in Veriliog? If, yes please let me know the section in Verilog Specification file where it is defined. Sometimes we use the following:

y = c | ({d, ( a | ~b)}) where a,b,c,d are inputs and y is an output.

Can anybody explain more on () ? Can this () be used to provide priority in evaluation as it is done in mathematics?

y= ( a | ~b) where a and b are inputs and y is an output?

The reason I ask this question because we are using parantheses () here and in Verilog specification file I am not able to find where () is defined. In the list of operator I do not find () is defined. Is it an allowed construct in Veriliog? If, yes please let me know the section in Verilog Specification file where it is defined. Sometimes we use the following:

y = c | ({d, ( a | ~b)}) where a,b,c,d are inputs and y is an output.

Can anybody explain more on () ? Can this () be used to provide priority in evaluation as it is done in mathematics?