soa

Newbie level 4

- Joined

- Nov 7, 2009

- Messages

- 6

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- United States

- Activity points

- 1,350

Dear All,

I am using IBM130nm technology,

when I want to check LVS, there is an error in mismatch between layout and schematic.

even if I use a single nfettw from standard library (cmrf8sf), the error remains the same.

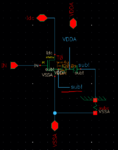

the error is in number of pins: in layout the nfettw has 4 pins for fet while in the schematic the nfettw has 6 pins

I think LVS checks just 4 pins in layouts (G D S B) and separates the NW contact as new component (subc).

I appreciate if somebody can help me.

Thanks a lot

I am using IBM130nm technology,

when I want to check LVS, there is an error in mismatch between layout and schematic.

even if I use a single nfettw from standard library (cmrf8sf), the error remains the same.

the error is in number of pins: in layout the nfettw has 4 pins for fet while in the schematic the nfettw has 6 pins

I think LVS checks just 4 pins in layouts (G D S B) and separates the NW contact as new component (subc).

I appreciate if somebody can help me.

Thanks a lot