Junus2012

Advanced Member level 5

dear friends

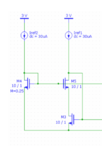

I am designing a folded cascode opam just like in the attached image,

I have question about this circuit, in typical folded cascode opamp we have current source and current mirror, but in this configuration we only have mirrors, one at the top and one at the bottom,

so how the currents at the output stage is summed, if we know that one of the current is comming from the differential tail current, the other one from where??

I am just thinking that the other current is from the floating current transistors but I am not sure, and if it is true the what are the rules for designing this circuit.

let us assume that I will use a differential tail current = 50 uA.

I would appreciate any kind of help

Thank you in advance

I am designing a folded cascode opam just like in the attached image,

I have question about this circuit, in typical folded cascode opamp we have current source and current mirror, but in this configuration we only have mirrors, one at the top and one at the bottom,

so how the currents at the output stage is summed, if we know that one of the current is comming from the differential tail current, the other one from where??

I am just thinking that the other current is from the floating current transistors but I am not sure, and if it is true the what are the rules for designing this circuit.

let us assume that I will use a differential tail current = 50 uA.

I would appreciate any kind of help

Thank you in advance