abaz

Member level 2

- Joined

- Apr 26, 2011

- Messages

- 51

- Helped

- 7

- Reputation

- 14

- Reaction score

- 7

- Trophy points

- 1,288

- Location

- Berkeley, Australia

- Activity points

- 1,609

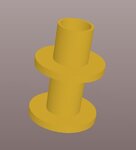

Taking into account my clearance constraints and polygon pours for power supply nets on a BGA device, I find that I'm not getting much connection metal between the vias that are not power supply ones.

If I have full stack vias going through a multi layer board and decide to remove via pads on layers that the via is just passing through is this a problem for PCB manufacturers or can they all do it. I'm particularly interested if this is possible on the top and bottom layers, where I can make the pad diameter the same as the hole size, giving me more width in my polygon pours or traces going inbetween vias

Any thoughts or experience on this matter would be greatly appreciated

If I have full stack vias going through a multi layer board and decide to remove via pads on layers that the via is just passing through is this a problem for PCB manufacturers or can they all do it. I'm particularly interested if this is possible on the top and bottom layers, where I can make the pad diameter the same as the hole size, giving me more width in my polygon pours or traces going inbetween vias

Any thoughts or experience on this matter would be greatly appreciated