henry kissinger

Member level 2

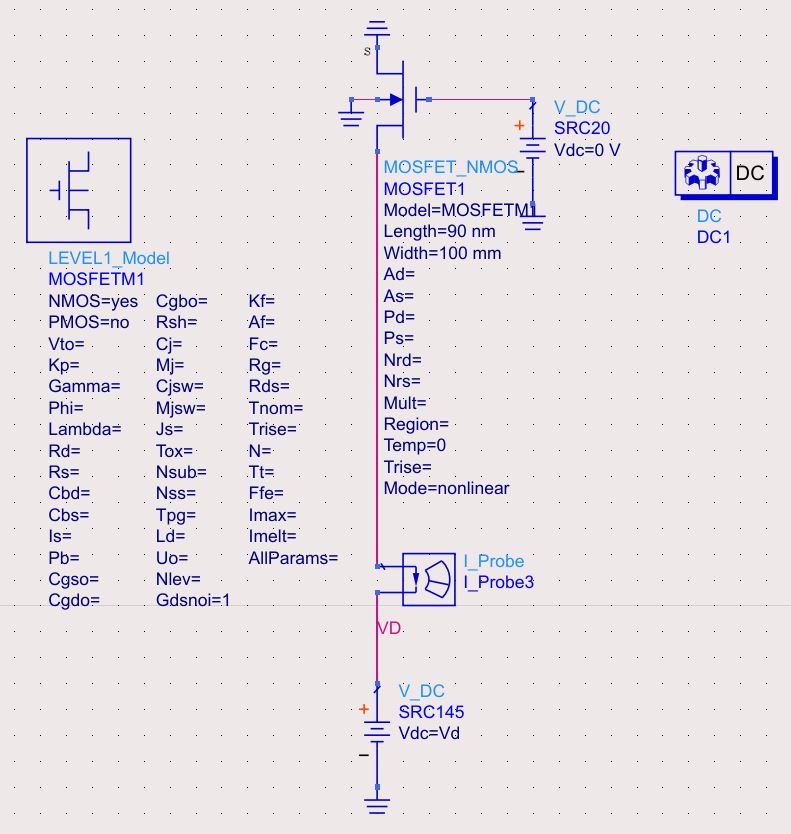

The NMOS configuration is as below.

the gate voltage is 0 V

the source voltage is fixed to 0 V, the drain voltage is swept from -2 V to 2V.

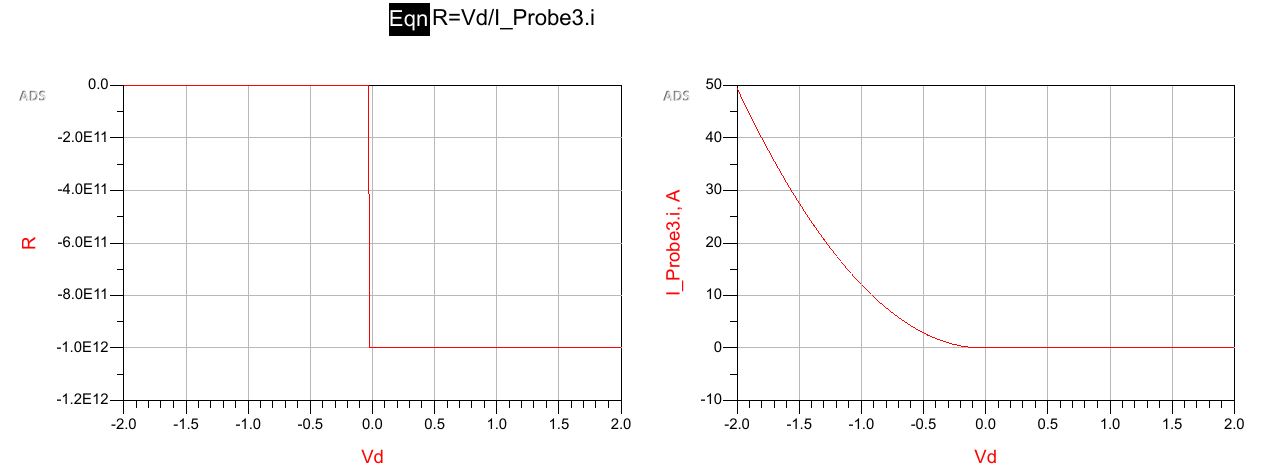

We can see that the threshold of voltage difference between source and drain is very little, at drain voltage around -0.01 V.

What parameter of this NMOS shown in the second graph (Level1_Model) I can change in order to have the threshold voltage difference much negative, say -10 V ?

the gate voltage is 0 V

the source voltage is fixed to 0 V, the drain voltage is swept from -2 V to 2V.

We can see that the threshold of voltage difference between source and drain is very little, at drain voltage around -0.01 V.

What parameter of this NMOS shown in the second graph (Level1_Model) I can change in order to have the threshold voltage difference much negative, say -10 V ?