pha0001m

Junior Member level 1

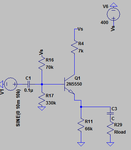

I am using the 2N5550 to build a simple buffer amplifier. This transistor has a Vce rating of 150V. I have constructed a circuit as attached bellow. This circuit will run on a 400V DC power supply.

I have tried to DC biased the transistor so that in the steady-state operating condition Vce is less than 40V. Thus, it should not blow up. However, what happen when the circuit is initially turn on? As I fear that the NPN will see the full 400V across at turn on. What do you guys think? Will this circuit work in practice?

Note: I do not want to cascode the transistor, nor do I want to use a NPN with a higher Vce rating.

I have tried to DC biased the transistor so that in the steady-state operating condition Vce is less than 40V. Thus, it should not blow up. However, what happen when the circuit is initially turn on? As I fear that the NPN will see the full 400V across at turn on. What do you guys think? Will this circuit work in practice?

Note: I do not want to cascode the transistor, nor do I want to use a NPN with a higher Vce rating.