Embedded Partner

Full Member level 5

- Joined

- Nov 29, 2010

- Messages

- 247

- Helped

- 42

- Reputation

- 84

- Reaction score

- 37

- Trophy points

- 1,308

- Location

- Hubli(INDIA)

- Activity points

- 2,636

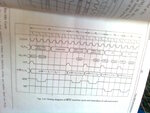

i 8085 microprocessor why the call instuction has highest T states for opcode fetch(i.e,6T states)?

---------- Post added at 05:12 ---------- Previous post was at 05:09 ----------

most of the instructions in 8085 are having only 4T states for the opcode fetch, why for call 6 T states?

---------- Post added at 05:12 ---------- Previous post was at 05:09 ----------

most of the instructions in 8085 are having only 4T states for the opcode fetch, why for call 6 T states?