vijaymishra

Newbie level 5

Hi,

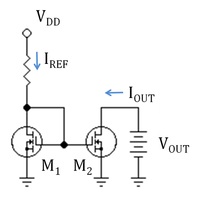

I case of a current mirror layout, the gate voltage line is under consideration. We are required not to route voltage lines for long.

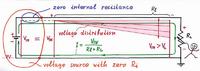

As per my understanding, the RC model [per suqare] of the metal track, acts like a RC network for the voltage source [Vgs].Depending on the RC time constant, it will charge and will tranfer the voltage to the next cap. Hence the voltage at the end of the line will be the same Vgs as that at the source. So what is the exact reason to keep the voltage route to minimum?

I case of a current mirror layout, the gate voltage line is under consideration. We are required not to route voltage lines for long.

As per my understanding, the RC model [per suqare] of the metal track, acts like a RC network for the voltage source [Vgs].Depending on the RC time constant, it will charge and will tranfer the voltage to the next cap. Hence the voltage at the end of the line will be the same Vgs as that at the source. So what is the exact reason to keep the voltage route to minimum?