jimmykk

Full Member level 3

Hi

I aM trying to get a short pulse of frequency 50khz with 5 cycles from MD1213. The problem i am getting is that i am able to get only a single output from OUTB while OUTA is at VH(5V) level and does not provide any pulse out of it. i am using Altera DE1 SOC board for logic and logic for INA, INB and OE (all are between 0 and 3.3v) are coming from this board + 5V supply voltage is PROVIDED TO VDD1, VDD2 and VH while VL, VSS1 and VSS2 are connected to ground. I am not sure whether it is a hardware problem or software. Anyways, i have attached my VHDL code for this. Please check and suggest some improvements.

I aM trying to get a short pulse of frequency 50khz with 5 cycles from MD1213. The problem i am getting is that i am able to get only a single output from OUTB while OUTA is at VH(5V) level and does not provide any pulse out of it. i am using Altera DE1 SOC board for logic and logic for INA, INB and OE (all are between 0 and 3.3v) are coming from this board + 5V supply voltage is PROVIDED TO VDD1, VDD2 and VH while VL, VSS1 and VSS2 are connected to ground. I am not sure whether it is a hardware problem or software. Anyways, i have attached my VHDL code for this. Please check and suggest some improvements.

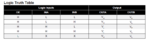

Code VHDL - [expand]

Last edited by a moderator: