brakchus

Newbie level 4

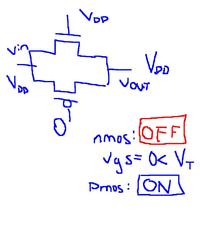

Hi, I have TG design as in the picture below:

**broken link removed**

while the enable and ~enable signals (at transistors gates) was from Virtuoso Analog Design Environment as stimuli signals, the output was just as I expected. After I added an inverter the output change. The result is in the picture below:

**broken link removed**

Can anybody give me a clue, why the output isn't always at gnd level? And sometimes even over vdd?

**broken link removed**

while the enable and ~enable signals (at transistors gates) was from Virtuoso Analog Design Environment as stimuli signals, the output was just as I expected. After I added an inverter the output change. The result is in the picture below:

**broken link removed**

Can anybody give me a clue, why the output isn't always at gnd level? And sometimes even over vdd?