Zac1

Member level 1

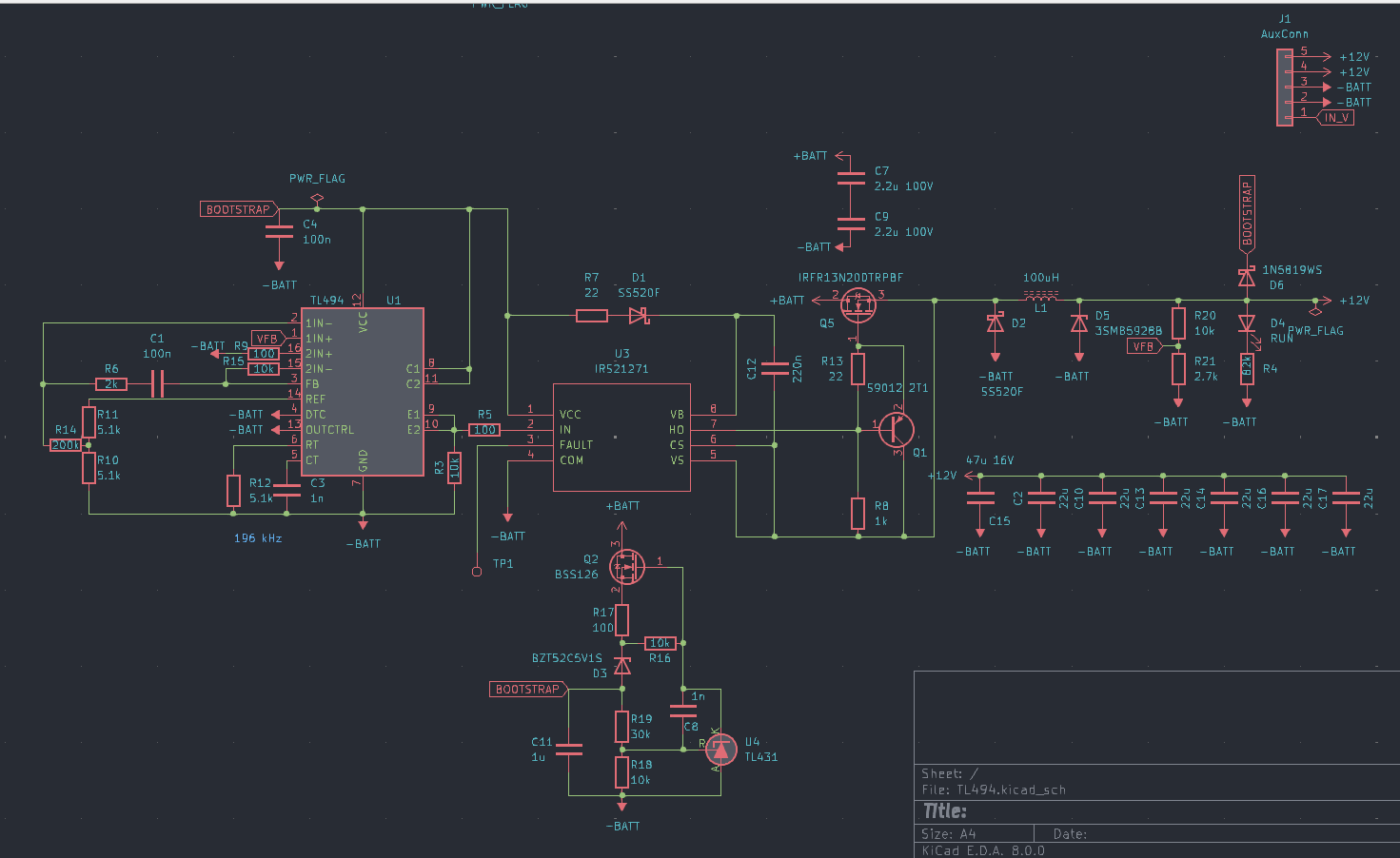

With a help of few people I managed to design fairly wide range DCDC converter using TL494

I confirmed it works in range of 30-190V DC

Has fairly stable 12V output with ~40mV peak to peak noise

Can deliver up to 3A.

However it has one fatal flaw that haunts me in my dreams. It kills mosfet Q5 and diode D2 if you suddenly apply 160V+ (high dV/dt)

It does work properly if slowly raising voltage across 40-190V. Also works up until 140V (sudden turn on).

I have managed to capture the problematic moment on thermal camera

Basically there is a full short on Q5 and D2 for a moment, then fuse pops and both components have dead short. I have tried to remedy this situation with help of PNP clamp (Q1) but it doesn't do much. I am out of ideas how to fix this... perhaps the driver is at fault? Or maybe diode is too slow?

I confirmed it works in range of 30-190V DC

Has fairly stable 12V output with ~40mV peak to peak noise

Can deliver up to 3A.

However it has one fatal flaw that haunts me in my dreams. It kills mosfet Q5 and diode D2 if you suddenly apply 160V+ (high dV/dt)

It does work properly if slowly raising voltage across 40-190V. Also works up until 140V (sudden turn on).

I have managed to capture the problematic moment on thermal camera

Basically there is a full short on Q5 and D2 for a moment, then fuse pops and both components have dead short. I have tried to remedy this situation with help of PNP clamp (Q1) but it doesn't do much. I am out of ideas how to fix this... perhaps the driver is at fault? Or maybe diode is too slow?