LONGGANG

Newbie level 4

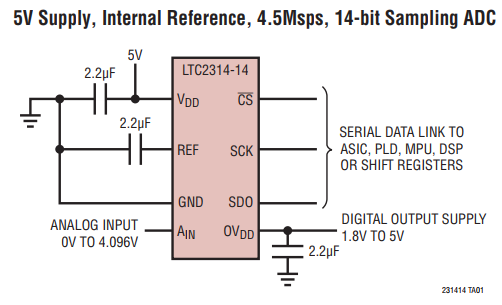

Hi, I am new to the ADC application. I am using the ADC LTC2314-14 for testing DC inputs and AC inputs.

The outside circuit is shown in the figure. For the SPI protocol, there are no issues inside the communication. The FPGA can read the correct SDO from the ADC, the SCK is 1MHZ which is also not high to cause some delay issues.

The outside circuit is shown in the figure. For the SPI protocol, there are no issues inside the communication. The FPGA can read the correct SDO from the ADC, the SCK is 1MHZ which is also not high to cause some delay issues.

The problem right now is that the potential stray capacitance between Ain and VDD. I have tested two same ADC and got the same results. When the analog input is a sin wave at 10HZ, the ADC shows a result with a constant gain 0.99. (For instance, sin changes from 0V to 1V. The ADC will give a result 0V to 0.99V). This gain ratio is not ideal but it is fixed during the whole sin period. So I can compensate for this by myself.

If the input is a DC voltage, the ADC results show different gain corresponding to different inputs. (For instance: for a 1.8V DC input, the ADC gave 1.782V outputs. But for a 0.5V DC input, the ADC will give 0.480V ) The gains are 0.99 and 0.96 respectively. This is impossible for a 14bits ADC with a maximum offset error around 4mV. During the test, the gain range will shrink from a high DC input (1.8V) to a low DC input (0.5V)(exp. : gains become 0.99 and 0.98) with a 20nF capacitor connecting from Ain () to the ground. But this gain range will shrink to a constant and cannot be decreased with a higher bypassing capacitor (From Ain to GND)anymore. :-(

In this case, I cannot only use this ADC for AC inputs by compensating for a constant gain. For DC inputs, I totally have no ideas about that. (DC should be super simple but it beat me )

Has anyone encountered the same problem or have good suggestions? Thank you very much!

BR,

LONGGANG

The problem right now is that the potential stray capacitance between Ain and VDD. I have tested two same ADC and got the same results. When the analog input is a sin wave at 10HZ, the ADC shows a result with a constant gain 0.99. (For instance, sin changes from 0V to 1V. The ADC will give a result 0V to 0.99V). This gain ratio is not ideal but it is fixed during the whole sin period. So I can compensate for this by myself.

If the input is a DC voltage, the ADC results show different gain corresponding to different inputs. (For instance: for a 1.8V DC input, the ADC gave 1.782V outputs. But for a 0.5V DC input, the ADC will give 0.480V ) The gains are 0.99 and 0.96 respectively. This is impossible for a 14bits ADC with a maximum offset error around 4mV. During the test, the gain range will shrink from a high DC input (1.8V) to a low DC input (0.5V)(exp. : gains become 0.99 and 0.98) with a 20nF capacitor connecting from Ain () to the ground. But this gain range will shrink to a constant and cannot be decreased with a higher bypassing capacitor (From Ain to GND)anymore. :-(

In this case, I cannot only use this ADC for AC inputs by compensating for a constant gain. For DC inputs, I totally have no ideas about that. (DC should be super simple but it beat me )

Has anyone encountered the same problem or have good suggestions? Thank you very much!

BR,

LONGGANG