jamesjjc

Newbie

Hi,

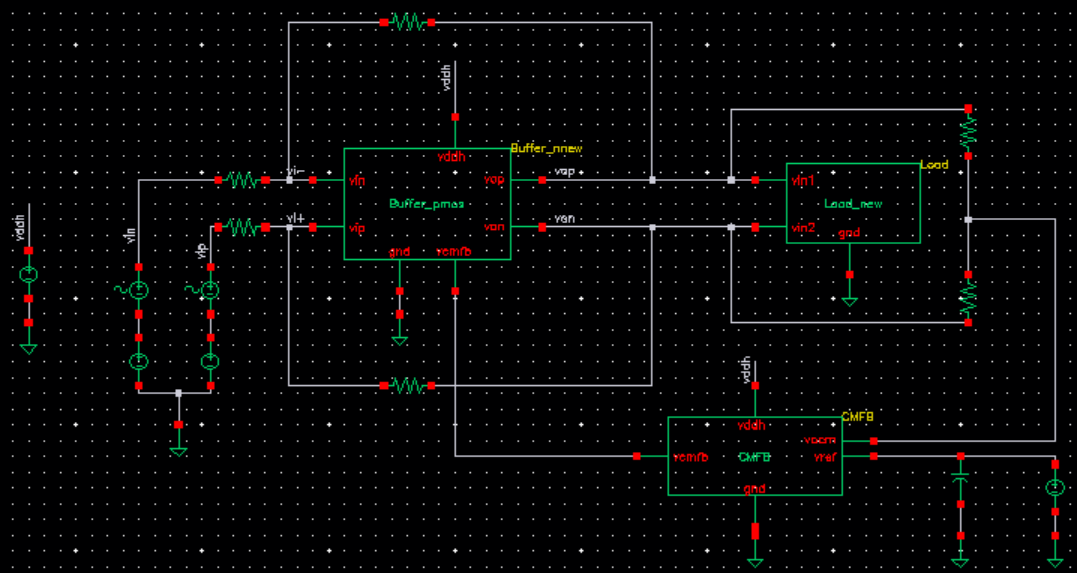

I'm designing a two-stage amplifier with a closed-loop gain of 2 to drive an ADC by 1.6Vpp differential output swing. The load is consisted of a RC filter and ADC input impedance, overall it's a 45ohm resistive load in parallel with 3pF capacitance.

The main goal is to achieve high linearity within a bandwidth of 650MHz. I'm targeting a SFDR>=66dB within the BW.

As far as I know, the linearity in my buffer is mainly determined by three factors:

1. Loop gain. If the loop gain is high enough, the signal swing inside my buffer can be suppressed by the negative feedback network.

2. Input pair linearity. It should be biased by high overdrive voltage Vod to achieve linear id/vgs (or constant gm).

3. Vod > Vdsat for each transistor. So that every device with be operated in saturation region.

4. Phase margin. If the PM is too small, the circuit might be suffered from the stabilty issue.

Based on the above, if the circuit is properly biased we can say that at higher frequency, the linearity decreases since the loop gain drops after the pole frequency. So I believe the SFDR will monotonically decrease when we increase the operating frequency.

My question is that when I simulate the SFDR with PSS in cadence spectre, I found that the SFDR drops, pops and then drops at high frequency. Anyone who can explain this? Or is there any other reason that can affect my SFDR?

Thanks, let me know if any other information is needed.

I'm designing a two-stage amplifier with a closed-loop gain of 2 to drive an ADC by 1.6Vpp differential output swing. The load is consisted of a RC filter and ADC input impedance, overall it's a 45ohm resistive load in parallel with 3pF capacitance.

The main goal is to achieve high linearity within a bandwidth of 650MHz. I'm targeting a SFDR>=66dB within the BW.

As far as I know, the linearity in my buffer is mainly determined by three factors:

1. Loop gain. If the loop gain is high enough, the signal swing inside my buffer can be suppressed by the negative feedback network.

2. Input pair linearity. It should be biased by high overdrive voltage Vod to achieve linear id/vgs (or constant gm).

3. Vod > Vdsat for each transistor. So that every device with be operated in saturation region.

4. Phase margin. If the PM is too small, the circuit might be suffered from the stabilty issue.

Based on the above, if the circuit is properly biased we can say that at higher frequency, the linearity decreases since the loop gain drops after the pole frequency. So I believe the SFDR will monotonically decrease when we increase the operating frequency.

My question is that when I simulate the SFDR with PSS in cadence spectre, I found that the SFDR drops, pops and then drops at high frequency. Anyone who can explain this? Or is there any other reason that can affect my SFDR?

| 10MHz | 100MHz | 300MHz | 400MHz | 500MHz | 600MHz | 700MHz | 800MHz | 900MHz | |||||||||||||||||||||

| SFDR (dB) | 82.34 | 68.88 | 66.45 | 66.99 | 67.27 | 72.54 | 76.11 | 62.43 | 56.09 |

Thanks, let me know if any other information is needed.