suquid29

Junior Member level 2

Same issue from last week, but exact requirements now

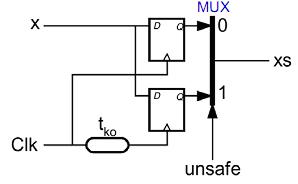

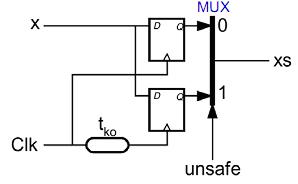

I want to imlement this very simple circuit on VirtexII-Pro:

When sampling asynchronous signal, you can enter metastability. In this simple

circuit, I sample both in clk and delayed clk. The delay time is actually t_ko=t_su+t_h, hence, one FF sampled correctly.

The problem is implementing the delay line.

According to VirtexII-Pro data sheet, t_su+t_h for general CLB is ~0.14 ns, depends on the speed grade, so i want to be able to implement a delay line with resolution of 0.01 ns. Is this possible??

According to the same doc, t_pd of LUT is ~0.23 ns, so cascade of NOT gates wont do it...

Thanks in advanced.

I want to imlement this very simple circuit on VirtexII-Pro:

When sampling asynchronous signal, you can enter metastability. In this simple

circuit, I sample both in clk and delayed clk. The delay time is actually t_ko=t_su+t_h, hence, one FF sampled correctly.

The problem is implementing the delay line.

According to VirtexII-Pro data sheet, t_su+t_h for general CLB is ~0.14 ns, depends on the speed grade, so i want to be able to implement a delay line with resolution of 0.01 ns. Is this possible??

According to the same doc, t_pd of LUT is ~0.23 ns, so cascade of NOT gates wont do it...

Thanks in advanced.