shanmei

Advanced Member level 1

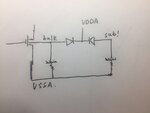

From the thread, https://www.edaboard.com/threads/264917/

which shows NMOS bulk and sub! connection.

I am wondering the whether the connection is right. The trip well NMOS device is used to isolate the bulk node and the noisy sub! node. In the above figure, the bulk and sub! are actually shorted together though the subc.

1. Then how can the bulk immune from the noisy sub!?

2. We can assume that the two terminals of the subc are short, right?

Thanks.

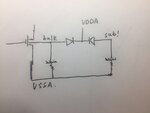

which shows NMOS bulk and sub! connection.

I am wondering the whether the connection is right. The trip well NMOS device is used to isolate the bulk node and the noisy sub! node. In the above figure, the bulk and sub! are actually shorted together though the subc.

1. Then how can the bulk immune from the noisy sub!?

2. We can assume that the two terminals of the subc are short, right?

Thanks.