fala

Full Member level 5

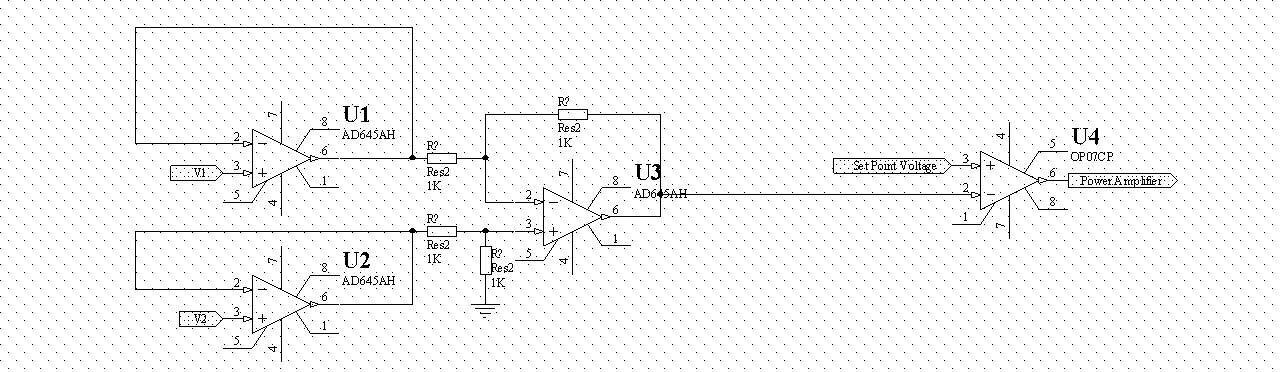

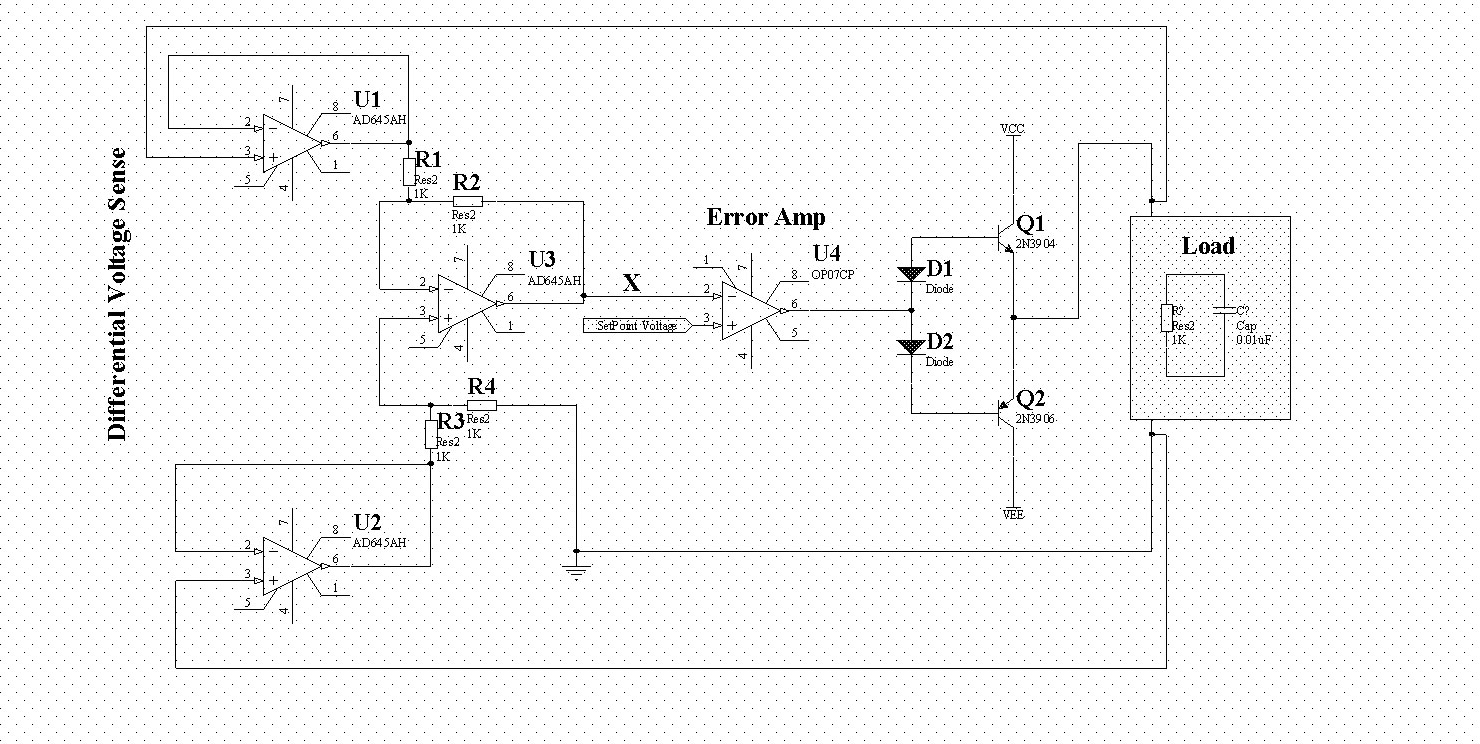

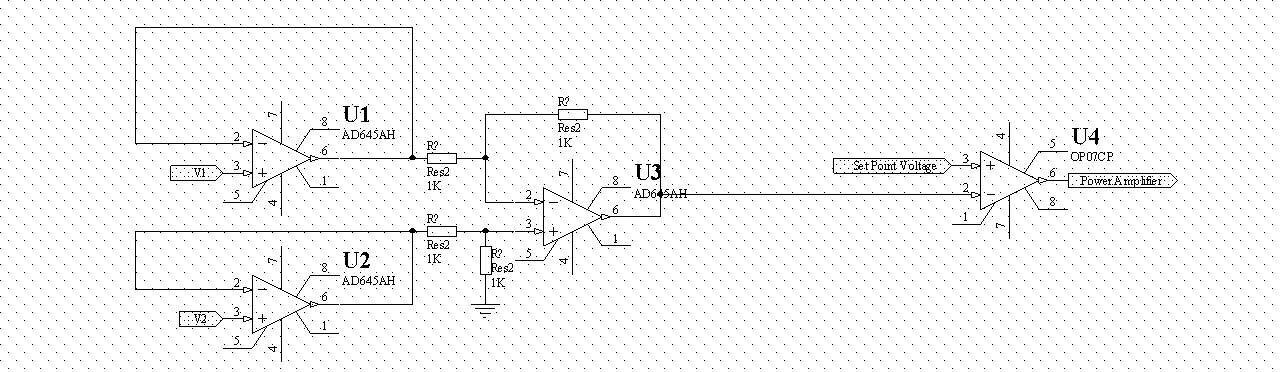

Hello, I have a circuit that measures voltage differentially and then by feeding the measured voltage to an error amplifier that has a fixed voltage at its non inverting pin completes the feedback loop of error amplifier. My question is what should I do to prevent instability of feed back loop because there are three opamps in the feedback path so if each opamp shift 60 degrees it means 180 degree shift and resonance. The load can have some capacitance and the capacitance of load is not known to me. So how should I stabilize the feedback loop. Input opamps should be low Ib fet opamps.

Should I put low pass filter between U3, U4??? Thank you very much

Should I put low pass filter between U3, U4??? Thank you very much