zorax85

Junior Member level 3

This is my question...

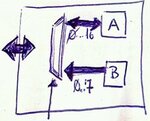

I have two modules and they share an I/O bus of 16 bits.

The first module, that we can call module A, needs to use all 16 bits in bidirectional mode.

The second module, that we can call module B, needs to use just 8 bits in output mode.

Which is the best solution in order to provide the normal use of the module A, and sometimes, using a bypass for example, enable the module B?

I have two modules and they share an I/O bus of 16 bits.

The first module, that we can call module A, needs to use all 16 bits in bidirectional mode.

The second module, that we can call module B, needs to use just 8 bits in output mode.

Which is the best solution in order to provide the normal use of the module A, and sometimes, using a bypass for example, enable the module B?