Junus2012

Advanced Member level 5

Dear friends

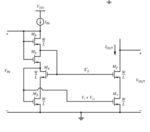

In my most circuits I use the wide swing current mirror for biasing my amplifier and most desingers use it specially for low voltage aplication.

However there is comparable mirror performance named the "Sooch current mirror" which I attached its image.

It is known that this circuit consume more headroom voltage at the input making it unapplicable for low voltage circuits, but from my hand calculation I still see that this circuit fine with 3.3 V CMOS technology which I am using so why this circuit is not common in this technology or above.

is there any other drawback that makes the wide swing mirror more preferable over it ?

Thank you very much

In my most circuits I use the wide swing current mirror for biasing my amplifier and most desingers use it specially for low voltage aplication.

However there is comparable mirror performance named the "Sooch current mirror" which I attached its image.

It is known that this circuit consume more headroom voltage at the input making it unapplicable for low voltage circuits, but from my hand calculation I still see that this circuit fine with 3.3 V CMOS technology which I am using so why this circuit is not common in this technology or above.

is there any other drawback that makes the wide swing mirror more preferable over it ?

Thank you very much