FAMA89

Newbie

Hi,

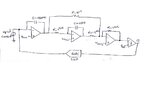

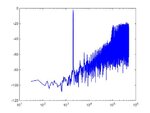

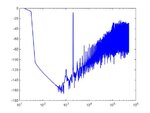

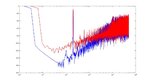

I am designing a 2nd order continuous time feedforward sigma delta where the input is current. the design parameters are: OSR=128, sampling frequency=1MHz, OTA gain=70dB, OTA UGBW=2.5MHz, NRZ DAC current=12uA. I have done the simulatin in Simulink/MATLAB achieving 87dB SNR. But, doing the transistor level simulation in Cadence, I am showing higher noise floor than what is supposed to be, so SNR is 63dB. The output voltages of the opamps are in the swing range, so the opamp saturation wouldn't be an issue. I have attached the sircuit schematic. I would appreciate if anyone could help me with that.

Using the same OTA and comparator, I have designed 2nd order CIFB sigma delta with 82dB SNR, but my problem is with CIFF sigma delta.

Thank you.

I am designing a 2nd order continuous time feedforward sigma delta where the input is current. the design parameters are: OSR=128, sampling frequency=1MHz, OTA gain=70dB, OTA UGBW=2.5MHz, NRZ DAC current=12uA. I have done the simulatin in Simulink/MATLAB achieving 87dB SNR. But, doing the transistor level simulation in Cadence, I am showing higher noise floor than what is supposed to be, so SNR is 63dB. The output voltages of the opamps are in the swing range, so the opamp saturation wouldn't be an issue. I have attached the sircuit schematic. I would appreciate if anyone could help me with that.

Using the same OTA and comparator, I have designed 2nd order CIFB sigma delta with 82dB SNR, but my problem is with CIFF sigma delta.

Thank you.