deardeepa76

Junior Member level 3

Dear All,

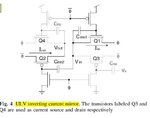

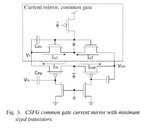

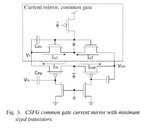

I am trying to simulate a semi-floating gate current mirror seen in fig1.

How to get the graph as output, what sweep should I make?

Fig 1

This is the netlist

I am trying to simulate a semi-floating gate current mirror seen in fig1.

How to get the graph as output, what sweep should I make?

Fig 1

This is the netlist

Code:

* CSFG Common gate current mirror recharge freq 100MHz

********* Simulation Settings - General section *********

.include "D:\HSPICE\NewCSFGBkup\t96w_9sf_9m_lb_3-params.txt"

********* Simulation Settings - Parameters and SPICE Options *********

*-------- Devices: SPICE.ORDER > 0 --------

CCinn V1 N_3 1p

CCinp1 In N_4 1p

CCinp2 Out N_5 1p

MNMOS_1 V1 N_3 Vdd1 Gnd CMOSN W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MNMOS_2 Out N_3 Vdd1 Gnd CMOSN W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MNMOS_3 N_4 Vdd1 Gnd Gnd CMOSN W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MNMOS_4 N_5 Vdd1 Gnd Gnd CMOSN W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MPMOS_1 N_3 Vdd2 Vdd Vdd CMOSP W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MPMOS_2 V1 N_4 Vdd2 Vdd CMOSP W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MPMOS_3 Out N_5 Vdd2 Vdd CMOSP W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

VVsupply Vdd Gnd DC 250m

VVf Vdd1 Gnd PULSE(0 1 0 3n 3n 10n 40n)

VVfbar Vdd2 Gnd PULSE(0 1 20n 3n 3n 10n 40n)

VVin In Gnd DC 1 SIN(.125 .125 2MEG)

********* Simulation Settings - Analysis section *********

.tran 100n 2u

.DC VVin 0 250m .0250

.print dc ID(MPMOS_2)

.print dc ID(MPMOS_3)

********* Simulation Settings - Additional SPICE commands *********

.end