celebrevida

Member level 2

I've been studying Fractional-N PLL design and learned that you can implement it using a first order DAC. Frac-N PLLs can divide by N+A/B.

You can do this by dividing by N for B-A reference clk cycles and N+1 for A cycles. The average Fvco/Fref is then (N+A/B)

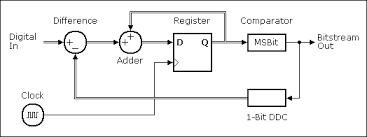

The first order DAC is as follows:

The operation is straightforward. Digital In is A. The 1-Bit DDC maps OUT=0 to 0 or OUT=1 to B. The Comparator outputs 0 if Reg < B and 1 if > B and overflows which also determines the 1-bit DDC value that gets subtracted. It's easy to hand-simulate and understand.

For instance, if A=3 and B=8, you have an OUT bitsteam of 00100101 (repeating)

Using 1st order DAC for Frac-N is usually not done because the frequency deviations from Fvco_target are large and noisy.

So I am aware that 2nd order Delta-Sigma modulator is used. This modulator has 2-bit output and can provide -1,0,1,2 (instead of 0 and 1 like first order) thus allowing division of N-1,N,N+1,N+2.

The problem is that I am having a lot of trouble finding documentation that allows me to understand 2nd order Delta-Sigma modulation for Frac-N PLL.

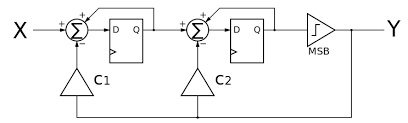

Here is one picture I found but there's not details on the theory or how it works.

For instance, how are you getting 2-bit output stream?

What exactly is going on when you cascade what looks like two 1st order delta-sigma back to back?

Appreciate any insight or any link to resources. I understand 1st order very well but just can't get my hands around 2nd order delta-sigma at all right now.

You can do this by dividing by N for B-A reference clk cycles and N+1 for A cycles. The average Fvco/Fref is then (N+A/B)

The first order DAC is as follows:

The operation is straightforward. Digital In is A. The 1-Bit DDC maps OUT=0 to 0 or OUT=1 to B. The Comparator outputs 0 if Reg < B and 1 if > B and overflows which also determines the 1-bit DDC value that gets subtracted. It's easy to hand-simulate and understand.

For instance, if A=3 and B=8, you have an OUT bitsteam of 00100101 (repeating)

Using 1st order DAC for Frac-N is usually not done because the frequency deviations from Fvco_target are large and noisy.

So I am aware that 2nd order Delta-Sigma modulator is used. This modulator has 2-bit output and can provide -1,0,1,2 (instead of 0 and 1 like first order) thus allowing division of N-1,N,N+1,N+2.

The problem is that I am having a lot of trouble finding documentation that allows me to understand 2nd order Delta-Sigma modulation for Frac-N PLL.

Here is one picture I found but there's not details on the theory or how it works.

For instance, how are you getting 2-bit output stream?

What exactly is going on when you cascade what looks like two 1st order delta-sigma back to back?

Appreciate any insight or any link to resources. I understand 1st order very well but just can't get my hands around 2nd order delta-sigma at all right now.